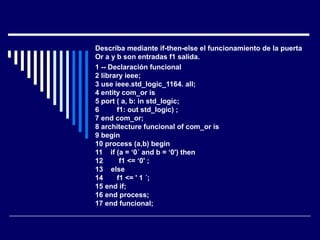

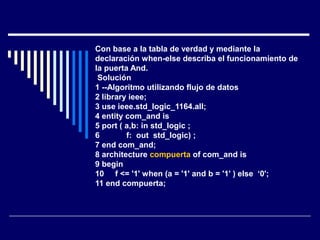

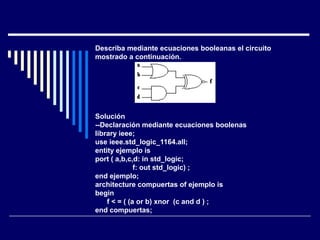

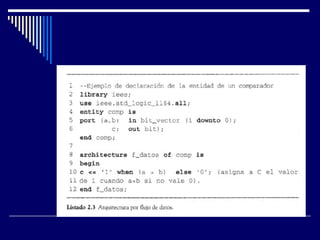

VHDL es un lenguaje que permite describir, analizar y evaluar el comportamiento de sistemas electrónicos digitales. Los programas en VHDL están compuestos de unidades de diseño como entidades, arquitecturas y configuraciones que definen la estructura y comportamiento del sistema. Las entidades representan los componentes electrónicos y sus conexiones, mientras que las arquitecturas describen su funcionamiento interno mediante declaraciones como procesos, funciones y ecuaciones booleanas.

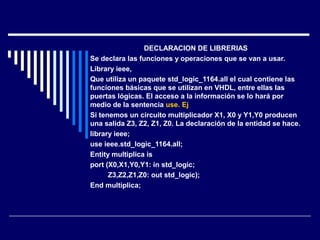

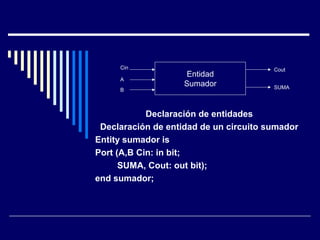

![Declaración de entidades

Declaración de entidad de un circuito sumador si A y B fuera de

4 bits

Entity sumador_4bits is

Port (A,B: in bit_vector (3 downto 0);

Cin: in bit;

SUMA: out bit_vector (3 downto 0);

Cout: out bit);

end sumador_4bits;

Entidad

Sumador 4bits

Cin

A[3:0]

B[3:0]

Cout

SUMA [3:0]](https://image.slidesharecdn.com/presentacin1vhdl-150421093319-conversion-gate01/85/Presentacion1vhdl-12-320.jpg)