555 Flipflop

- 1. A. Hermosa El circuito integrado 555 A2.1 Introducción El CI 555 es un circuito muy popular dada su versatilidad como generador de señales. Mediante unos pocos componentes externos, permite eficaces aplicaciones, básicamente, como generador de impulsos (clock) y como monoestable (temporizador). Puede funcionar con una tensión de alimentación entre unos 4,5 y 18 V y tiene una alta cargabilidad de salida (puede proporcionar una corriente de 200 mA). Asimismo, es muy estable térmicamente y bastante inmune a las variaciones de la tensión de alimentación. En su versión clásica aparece en un encapsulado DIL de 8 patillas, de tecnología bipolar. Posteriormente apareció el modelo 556, en formato de DIL de 14 patillas, que contiene dos circuitos 555 idénticos. Existe también en tecnología CMOS (por ejemplo, el TLC555, de Texas Instruments ). En su versión clásica, tecnología bipolar, la corriente típica de consumo (ICC) es de unos 3 mA (para VCC = 5 V). En tecnología CMOS el consumo es de sólo unos 100 µA (VDD = 5 V), aunque en contrapartida tiene menos cargabilidad de salida (además de otras diferencias respecto a la versión bipolar, que puede ser necesario tener en cuenta en ciertas aplicaciones). A2.2 Estructura interna En la figura A2.1 se muestra su estructura interna y del patillaje del CI en su versión más popular (DIL de 8 patillas). La estructura interna del 555 se basa en dos comparadores de tensión, un biestable SR activado por niveles, un transistor de descarga y la etapa de salida (buffer).

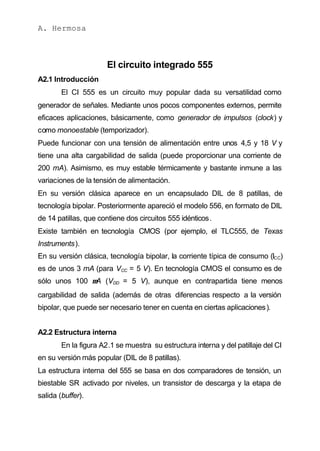

- 2. A. Hermosa Un divisor resistivo, compuesto por las tres resistencias R (de 5 KΩ), produce dos tensiones de referencia: V1 = 1/3 Vcc V2 = 2/3 Vcc Constituyen las tensiones de comparación de los comparadores. Los dos comparadores controlan el estado del biestable SR y en consecuencia el estado de la salida (patilla 3). + VCC 8 R Umbral Control 6 5 V2 R Disparo Comparador 2 2 Buffer R Salida Biestable Comparador 1 CL Q S V1 3 Q R Descarga 7 1 4 GND Reset a) GND 1 Disparo 2 Salida 3 Reset 4 8 7 Descarga 6 Umbral 5 555 + VCC Control b) Figura A2.1. a) Estructura interna del 555. b) Formato de encapsulado más popular.

- 3. A. Hermosa Asimismo, el biestable actúa sobre un transistor NPN de salida cuya saturación permite la descarga de un condensador exterior. El circuito de salida, buffer, es controlado por el biestable y se pueden obtener 200 mA. A2.2.1 Señales de control El control del circuito se realiza mediante las entradas umbral y disparo. Tensión umbral (patilla 6): La patilla umbral es la entrada no inversora del comparador 2. En la otra entrada del comparador, la inversora, se encuentra la tensión de referencia V2 = 2/3 Vcc. Cuando la tensión en la entrada umbral (patilla 6) es superior a 2/3 VCC, la salida del comparador activa la entrada R del biestable y en consecuencia la salida Q pasa a nivel bajo y la Q a nivel alto; esto hace que la salida (patilla 3) se ponga a potencial de masa (0 V) y, a la vez, se sature el transistor de descarga (con lo cual la patilla 7 también se pone a potencial de masa). Así, pues: Tensión umbral > 2 VCC 3 ⇒ Patilla 3 (Salida) = 0 V Patilla 7(Descarga) = 0 V Tensión de disparo (patilla 2): Esta entrada constituye la entrada inversora del comparador 1. En la otra entrada del comparador se encuentra la tensión de referencia V1 = 1/3 Vcc. Cuando la tensión en la patilla 2 desciende por debajo de 1/3 de Vcc , el comparador activa la entrada S del biestable y esto hace que Q = 1 y Q = 0 ; o sea, la salida (patilla 3) se pone a nivel alto (≅ VCC ) y se bloquea el

- 4. A. Hermosa transistor de descarga (con lo cual la patilla 7 se pone en estado de alta impedancia, colector abierto). Tensión disparo < 1 VCC ⇒ 3 Patilla 3 (Salida) ≅ VCC Patilla 7(Descarga) = Colector abierto Reset (patilla 4): Esta entrada, activa por nivel bajo (< 1V), es de estado prioritario y fuerza el biestable al estado Q = 0 , Q = 1 ; la salida (patilla 3) pasa a nivel bajo y se satura el transistor de descarga (patilla 7 a masa), se hace un reset. Reset < 1V ⇒ Patilla 3 (Salida) ≅ 0 V Patilla 7(Descarga) ≅ 0 V Tensión de control (patilla 5): Esta entrada permite modificar los niveles de tensión de referencia, aplicando un tensión externa. Tiene utilidad para hacer modulaciones, controles de frecuencia por tensión. Cuando no se utiliza, esta entrada se desacopla a masa por medio de un condensador típicamente de 100 nF.