Microprocesadores AMD e INTEL

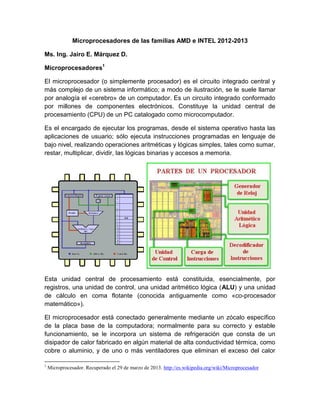

- 1. Microprocesadores de las familias AMD e INTEL 2012-2013 Ms. Ing. Jairo E. Márquez D. Microprocesadores1 El microprocesador (o simplemente procesador) es el circuito integrado central y más complejo de un sistema informático; a modo de ilustración, se le suele llamar por analogía el «cerebro» de un computador. Es un circuito integrado conformado por millones de componentes electrónicos. Constituye la unidad central de procesamiento (CPU) de un PC catalogado como microcomputador. Es el encargado de ejecutar los programas, desde el sistema operativo hasta las aplicaciones de usuario; sólo ejecuta instrucciones programadas en lenguaje de bajo nivel, realizando operaciones aritméticas y lógicas simples, tales como sumar, restar, multiplicar, dividir, las lógicas binarias y accesos a memoria. Esta unidad central de procesamiento está constituida, esencialmente, por registros, una unidad de control, una unidad aritmético lógica (ALU) y una unidad de cálculo en coma flotante (conocida antiguamente como «co-procesador matemático»). El microprocesador está conectado generalmente mediante un zócalo específico de la placa base de la computadora; normalmente para su correcto y estable funcionamiento, se le incorpora un sistema de refrigeración que consta de un disipador de calor fabricado en algún material de alta conductividad térmica, como cobre o aluminio, y de uno o más ventiladores que eliminan el exceso del calor 1 Microprocesador. Recuperado el 29 de marzo de 2013. http://es.wikipedia.org/wiki/Microprocesador

- 2. absorbido por el disipador. Entre el ventilador y la cápsula del microprocesador usualmente se coloca pasta térmica para mejorar la conductividad del calor. Existen otros métodos más eficaces, como la refrigeración líquida o el uso de células peltier para refrigeración extrema, aunque estas técnicas se utilizan casi exclusivamente para aplicaciones especiales, tales como en las prácticas de overclocking. La medición del rendimiento de un microprocesador es una tarea compleja, dado que existen diferentes tipos de "cargas" que pueden ser procesadas con diferente efectividad por procesadores de la misma gama. Una métrica del rendimiento es la frecuencia de reloj que permite comparar procesadores con núcleos de la misma familia, siendo este un indicador muy limitado dada la gran variedad de diseños con los cuales se comercializan los procesadores de una misma marca y referencia. Un sistema informático de alto rendimiento puede estar equipado con varios microprocesadores trabajando en paralelo, y un microprocesador puede, a su vez, estar constituido por varios núcleos físicos o lógicos. Un núcleo físico se refiere a una porción interna del microprocesador cuasi-independiente que realiza todas las actividades de una CPU solitaria, un núcleo lógico es la simulación de un núcleo físico a fin de repartir de manera más eficiente el procesamiento. Existe una tendencia de integrar el mayor número de elementos dentro del propio procesador, aumentando así la eficiencia energética y la miniaturización. Entre los elementos integrados están las unidades de punto flotante, controladores de la memoria RAM, controladores de buses y procesadores dedicados de video. Desde el punto de vista lógico, singular y funcional, el microprocesador está compuesto básicamente por: varios registros, una unidad de control, una unidad aritmético lógica, y dependiendo del procesador, puede contener una unidad de coma flotante.

- 3. El microprocesador ejecuta instrucciones almacenadas como números binarios organizados secuencialmente en la memoria principal. La ejecución de las instrucciones se puede realizar en varias fases: Prefetch, prelectura de la instrucción desde la memoria principal. Fetch, envío de la instrucción al decodificador Decodificación de la instrucción, es decir, determinar qué instrucción es y por tanto qué se debe hacer. Lectura de operandos (si los hay). Ejecución, lanzamiento de las máquinas de estado que llevan a cabo el procesamiento. Escritura de los resultados en la memoria principal o en los registros. Cada una de estas fases se realiza en uno o varios ciclos de CPU, dependiendo de la estructura del procesador, y concretamente de su grado de segmentación. La duración de estos ciclos viene determinada por la frecuencia de reloj, y nunca podrá ser inferior al tiempo requerido para realizar la tarea individual (realizada en un solo ciclo) de mayor coste temporal. El microprocesador se conecta a un circuito PLL, normalmente basado en un cristal de cuarzo capaz de generar pulsos a un ritmo constante, de modo que genera varios ciclos (o pulsos) en un segundo. Este reloj, en la actualidad, genera miles de megahercios. Rendimiento El rendimiento del procesador puede ser medido de distintas maneras, hasta hace pocos años se creía que la frecuencia de reloj era una medida precisa, pero ese mito, conocido como «mito de los megahertzios» se ha visto desvirtuado por el hecho de que los procesadores no han requerido frecuencias más altas para aumentar su potencia de cómputo. Durante los últimos años esa frecuencia se ha mantenido en el rango de los 1,5 GHz a 4 GHz, dando como resultado procesadores con capacidades de proceso mayores comparados con los primeros que alcanzaron esos valores. Además la tendencia es a incorporar más núcleos dentro de un mismo encapsulado para aumentar el rendimiento por medio de una computación paralela, de manera que la velocidad de reloj es un indicador menos fiable aún. De todas maneras, una forma fiable de medir la potencia de un procesador es mediante la obtención de las Instrucciones por ciclo Medir el rendimiento con la frecuencia es válido únicamente entre procesadores con arquitecturas muy similares o iguales, de manera que su funcionamiento interno sea el mismo: en ese caso la frecuencia es un índice de comparación válido. Dentro de una familia de procesadores es común encontrar distintas

- 4. opciones en cuanto a frecuencias de reloj, debido a que no todos los chip de silicio tienen los mismos límites de funcionamiento: son probados a distintas frecuencias, hasta que muestran signos de inestabilidad, entonces se clasifican de acuerdo al resultado de las pruebas. Esto se podría reducir en que los procesadores son fabricados por lotes con diferentes estructuras internas atendiendo a gamas y extras como podría ser una memoria caché de diferente tamaño, aunque no siempre es así y las gamas altas difieren muchísimo más de las bajas que simplemente de su memoria caché. Después de obtener los lotes según su gama, se someten a procesos en un banco de pruebas, y según su soporte a las temperaturas o que vaya mostrando signos de inestabilidad, se le adjudica una frecuencia, con la que vendrá programada de serie, pero con prácticas de overclock se le puede incrementar. La capacidad de un procesador depende fuertemente de los componentes restantes del sistema, sobre todo del chipset, de la memoria RAM y del software. Pero obviando esas características puede tenerse una medida aproximada del rendimiento de un procesador por medio de indicadores como la cantidad de operaciones de coma flotante por unidad de tiempo FLOPS, o la cantidad de instrucciones por unidad de tiempo MIPS2 . 2 MIPS es la abreviación de las palabras "Millones de Instrucciones Por Segundo". Es una forma de medir la potencia de los procesadores. Sin embargo, esta medida sólo es útil para comparar procesadores con el mismo juego de instrucciones y usando benchmarks que fueron compilados por el mismo compilador y con el mismo nivel de optimización. Esto es debido a que la misma tarea puede necesitar un número de instrucciones diferentes si los juegos de instrucciones también lo son; y por motivos similares en las otras dos situaciones

- 5. Una medida exacta del rendimiento de un procesador o de un sistema, es muy complicada debido a los múltiples factores involucrados en la computación de un problema, por lo general las pruebas no son concluyentes entre sistemas de la misma generación. Arquitectura El microprocesador tiene una arquitectura parecida a la computadora digital. En otras palabras, el microprocesador es como la computadora digital porque ambos realizan cálculos bajo un programa de control. Consiguientemente, la historia de la computadora digital ayuda a entender el microprocesador. El hizo posible la fabricación de potentes calculadoras y de muchos otros productos. El microprocesador utiliza el mismo tipo de lógica que es usado en la unidad procesadora central (CPU) de una computadora digital. El microprocesador es algunas veces llamado unidad microprocesadora (MPU). En otras palabras, el microprocesador es una unidad procesadora de datos. En un microprocesador se puede diferenciar diversas partes: Encapsulado: es lo que rodea a la oblea de silicio en sí, para darle consistencia, impedir su deterioro (por ejemplo, por oxidación por el aire) y permitir el enlace con los conectores externos que lo acoplaran a su zócalo a su placa base. Memoria caché: es una memoria ultrarrápida que emplea el procesador para tener alcance directo a ciertos datos que «predeciblemente» serán utilizados en las siguientes operaciones, sin tener que acudir a la memoria RAM, reduciendo así el tiempo de espera para adquisición de datos. Todos los micros compatibles con PC poseen la llamada caché interna de primer nivel o L1; es decir, la que está dentro del micro, encapsulada junto a él. Los micros más modernos (Core i3, Core i5, Core i7 de tercer generación y próximamente de cuarta generación.) incluyen descritas. En las comparativas, usualmente se representan los valores de pico, por lo que la medida no es del todo realista. La forma en que funciona la memoria que usa el procesador también es un factor clave para la potencia de un procesador, algo que no suele considerarse en los cálculos con MIPS. Debido a estos problemas, los investigadores han creado pruebas estandarizadas tales como SpecInt para medir el funcionamiento real, y las MIPS han caído en desuso. En el mundo de GNU/Linux se suelen referir a los MIPS como 'BogoMips'. El equivalente en la aritmética de punto flotante de los MIPS es el flops. Muchos microprocesadores de 8 y 16 bits han sido medidos con KIPS (kiloinstrucciones por segundo), que equivale a 0'001 MIPS. El primer microprocesador de propósito general, el Intel 8080 ejecutaba 640 KIPS. El Intel 8086 (16 bits), el primer microprocesador usado en PC, 800 KIPS. El Pentium 4 llega aproximadamente a 1'700 MIPS. Los PC actuales realizan un máximo de 18.000 millones de operaciones lógicas por segundo. Si se ejecutan 6 instrucciones por ciclo y hay 3.000 millones de ciclos por segundo, se tienen 18.000 MIPS.

- 6. también en su interior otro nivel de caché, más grande, aunque algo menos rápida, es la caché de segundo nivel o L2 e incluso los hay con memoria caché de nivel 3, o L3. Coprocesador matemático: unidad de coma flotante. Es la parte del micro especializada en esa clase de cálculos matemáticos, antiguamente estaba en el exterior del procesador en otro chip. Esta parte está considerada como una parte «lógica» junto con los registros, la unidad de control, memoria y bus de datos. Registros: son básicamente un tipo de memoria pequeña con fines especiales que el micro tiene disponible para algunos usos particulares. Hay varios grupos de registros en cada procesador. Un grupo de registros está diseñado para control del programador y hay otros que no son diseñados para ser controlados por el procesador pero que la CPU los utiliza en algunas operaciones, en total son treinta y dos registros. Memoria: es el lugar donde el procesador encuentra las instrucciones de los programas y sus datos. Tanto los datos como las instrucciones están almacenados en memoria, y el procesador las accede desde allí. La memoria es una parte interna de la computadora y su función esencial es proporcionar un espacio de almacenamiento para el trabajo en curso. Puertos: es la manera en que el procesador se comunica con el mundo externo. Un puerto es análogo a una línea de teléfono. Cualquier parte de la circuitería de la computadora con la cual el procesador necesita comunicarse, tiene asignado un «número de puerto» que el procesador utiliza como si fuera un número de teléfono para llamar circuitos o a partes especiales. Buses del procesador Todos los procesadores poseen un bus principal o de sistema por el cual se envían y reciben todos los datos, instrucciones y direcciones desde los integrados del chipset o desde el resto de dispositivos. Como puente de conexión entre el procesador y el resto del sistema, define mucho del rendimiento del sistema, su velocidad se mide en bits por segundo. Ese bus puede ser implementado de distintas maneras, con el uso de buses seriales o paralelos y con distintos tipos de señales eléctricas. La forma más antigua es el bus paralelo en el cual se definen líneas especializadas en datos, direcciones y para control. En la arquitectura tradicional de Intel (usada hasta modelos recientes), ese bus se llama front-side bus y es de tipo paralelo con 64 líneas de datos, 32 de direcciones además de múltiples líneas de control que permiten la transmisión de datos entre

- 7. el procesador y el resto del sistema. Este esquema se ha utilizado desde el primer procesador de la historia, con mejoras en la señalización que le permite funcionar con relojes de 333 Mhz haciendo 4 transferencias por ciclo.5 En algunos procesadores de AMD y en el Intel Core i7 se han usado otros tipos para el bus principal de tipo serial. Entre estos se encuentra el bus HyperTransport de AMD, que maneja los datos en forma de paquetes usando una cantidad menor de líneas de comunicación, permitiendo frecuencias de funcionamiento más altas y en el caso de Intel, Quickpath Los microprocesadores de Intel y de AMD (desde antes) poseen además un controlador de memoria de acceso aleatorio en el interior del encapsulado lo que hace necesario la implementación de buses de memoria del procesador hacia los módulos. Ese bus está de acuerdo a los estándares DDR de JEDEC y consisten en líneas de bus paralelo, para datos, direcciones y control. Dependiendo de la cantidad de canales pueden existir de 1 a 4 buses de memoria. AMD Bulldozer Es el nombre de la Arquitectura o tecnología de cómputo que AMD ha desarrollado para implementar en sus procesadores AMD FX-Series (nombre clave Zambezi).

- 8. Esta nueva arquitectura se basa en un proceso de manufactura de 32nm producido en las fábricas de Global Foundries bajo tecnología SOI (Silicon On Insulator). AMD primero ha destinado esta arquitectura a sus procesadores para el segmento de servidores, equivalente a los procesadores Opteron 6200 (Interlagos) y Opteron 4200 series (Valencia) de socket G34 socket C32 respectivamente. Ahora la arquitectura finalmente llega con sus procesadores AMD FX-series (Zambezi). Arquitectura: En lo primero en que AMD ha hecho hincapié, es que Bulldozer es totalmente diferente en su diseño, de hecho no se basa en los principios de la actual arquitectura K10.5 (Starts generation), que a su vez es una evolución de la anterior arquitectura K8. Bulldozer en su diseño posee diseño modular con componentes compartidos como dedicados. El diseño modular ha hecho rediseñar y reacomodar los elementos de la arquitectura de Bulldozer, enfocándose en optimizar el rendimiento, el consumo y en aprovechar al máximo el área del silicio donde viene integrado el procesador. Bulldozer, por lo tanto, ha sido diseñado para brindar un balance en rendimiento, costo y consumo en aplicaciones multi-threaded. La arquitectura se enfoca en poder suministrar altas frecuencias y recursos compartidos para lograr un óptimo rendimiento y poder potenciar la próxima generación de aplicaciones. En este sentido AMD ha indicado que mientras más nuevas sean las aplicaciones mejor aprovecharan el rendimiento de los procesadores AMD-FX. El set de instrucciones agregado también apunta en este sentido. El modelo tope de la nueva familia cuenta con 8-nucleos agrupado en cuatro módulos dual-core de diseño monolítico, está fabricado en 32nm y cuenta con un

- 9. conteo de transistores de aproximadamente 2 mil millones con un área física de 315mm2 . Esta arquitectura es la primera generación de nuevos núcleos de ejecución de AMD (La familia 15°) en la que ya se ha visto en los respectivos roadmap que a futuro AMD pretende renovar sus arquitecturas, incrementando el rendimiento por núcleo en cada generación. Dentro de los aspectos generales se tiene que Bulldozer cuenta con 128KB de memoria cache de nivel 1 (L1), 2MB de cache L2 compartido para cada núcleo y dedicado para cada módulo (8MB L2 en total) y 2MB de memoria cache L3 compartida para cada módulo (8MB de L3 en total). El resto de los componentes tenemos el bloque Fron-End y los 4 módulos “Bulldozer” (dual-core), controlador de memoria DDR3 de doble canal de 72-bits y 4 enlaces HyperTransport. Diseño de Arquitectura Modular: Los procesadores basados en esta arquitectura cuentan con un diseño modular, donde cada chip o núcleo está compuesto por múltiples módulos “Bulldozer” (4 en los modelos tope) con lo que AMD ofrecerá modelos de 4, 6 y 8 núcleos.

- 10. Analizando la naturaleza de las aplicaciones actuales, AMD encontró una forma de maximizar el ancho de banda tope a través de los diferentes núcleos y maximizar el uso de área de silicio del chip a través del uso de elementos o módulos compartidos. El resultado fue entonces diseñar módulos o bloques de doble núcleo, que pueden efectivamente optimizar los recursos dentro del procesador. Funciones con un alto grado de uso (como la unidad de enteros y el cache L1) son dedicados en cada núcleo. Mientras que otras unidades ahora están efectivamente compartidas entre los dos núcleos de cada módulo, incluyendo las unidades Fetch, Decode, los enrutamientos (pipelines) de la unidad de punto flotante y los niveles de cache L2.

- 11. Este nuevo diseño permite a ambos núcleos de cada módulo usar funciones más grandes y de alto rendimiento (como la unidad de punto flotante) y al mismo tiempo permite optimizar espacio en la pieza de silicio al estar en un módulo, en lugar de estar separados. En el diseño modular cada componente tiene elementos dedicados, también elementos compartidos a nivel de modulo y elementos compartidos a nivel de chip, dependiendo del orden jerárquico. Por ejemplo cada core o núcleo tiene su pequeño y respectivo cache dedicado de nivel1 (L1), a su vez incorpora 4 unidades de cálculo de enteros, a nivel de modulo cada núcleo comparte memoria cache L2, comparte también las dos unidades de cálculo de punto flotante, el decode (decodificador) y la unidad Fetch. A nivel de chips comparten la memoria cache L3 y el northbridge, que también se ha movido dentro del procesador, especialmente para la gestión del enrutamiento PCI Express3 , y el controlador de memorias que es otro componente compartido a nivel de chip. Elementos dedicados y compartidos: Los componentes internos de la arquitectura de Bulldozer pueden ser elementos compartidos (shared) que trae beneficios como: la reducción de consumo y temperatura, reduce el espacio físico del núcleo, y pueden ser también elementos dedicados que ayuda a incrementar 3 PCI Express (anteriormente conocido por las siglas 3GIO, en el caso de las "Entradas/Salidas de Tercera Generación", en inglés: 3rd Generation In/Out) es un nuevo desarrollo del bus PCI que usa los conceptos de programación y los estándares de comunicación existentes, pero se basa en un sistema de comunicación serie mucho más rápido. Este sistema es apoyado principalmente por Intel, que empezó a desarrollar el estándar con nombre de proyecto Arapahoe después de retirarse del sistema Infiniband.

- 12. el rendimiento y la escalabilidad. Así mismo Bulldozer puede cambiar dinámicamente entre los componentes compartidos como dedicados para maximizar el rendimiento por watts. Unidad de Punto Flotante y Enteros: La unidad de cálculo de enteros y punto flotante son dos aspectos o elementos de cálculo y cómputo muy importantes que definen el rendimiento de un procesador en aspectos específicos, ambas son unidades críticas en un procesador y potencian en cálculos de operaciones matemáticas y operaciones de cálculo propiamente dicho. AMD con Bulldozer ha hecho hincapié en este aspecto incorporando 2 unidades de cálculo de enteros por modulo (una para cada núcleo) con 4 pipelines (8 en

- 13. total). Esta unidad tiene su propio cache L1 dedicado. Esto se contrasta con las 3 unidades (pipelines) de la generación K10. Estas dos unidades comparten una interfaz común de punto flotante que actúa como programador. Cada módulo también incorpora dos unidades FMACs de 128-bit, cada uno de estos elementos posee 2 bloques de cache L1 dedicados. Estas unidades de 128-bit permiten instrucciones de 128-bit por núcleo o instrucciones de 256-bit por cada módulo dual-core Nuevas Instrucciones x86: Bulldozer a diferencia de la generación actual de procesadores AMD (Phenom II) también agrega el soporte para nuevas instrucciones de cómputo x86, entre las que se puede mencionar SSE3, SSE4.1, SSSE4.2 y las instrucciones AVX (Advanced Vector Extensions o Extensiones de

- 14. Vector Avanzadas) las cuales AMD implementa por primera vez en sus chip. Este set y/o sub-set de instrucciones también incluyendo 4 FMAC Operando, Registros YMM de 256-bit y AES; XSAVE e instrucciones XOP. Bulldozer también soportara la tecnología LWP (Light Weight Profiling). La adición de estas instrucciones le permite a los procesadores AMD-FX ponerse a la par con los procesadores Sandy Bridge de Intel y marcar una clara diferencia con los Phenom II que no soportan ninguna de estas nuevas instrucciones que AMD ha agregado a Bulldozer.

- 15. Los beneficios de agregar este nuevo set de instrucciones son bien específicos, pero los beneficios más cercanos al uso cotidiano en aplicaciones son sin lugar a dudas las instrucciones SSSE3, SSE4.1, SSE4.2 y AVX, soportadas tanto por AMD como por Intel, que permiten acelerar por ejemplo las tareas de codificación y decodificación de video, entre otras tareas como algoritmos biométricos y aplicaciones altamente intensivas en texto. En la siguiente tabla se observan las aplicaciones o ámbitos en los cuales se hace uso de estas instrucciones, cabe destacar que a pesar que la mayoría de las instrucciones agregadas en Bulldozer, ya estaban presentes en Sandy Bridge, AMD se adjudica la exclusividad de dos de ellas, como las instrucciones FMA4 que rinden sus beneficios en aplicaciones HTC (High-Performance Computing o Computación de alto rendimiento) y también las instrucciones XOP para aplicaciones numéricas, multimedia y algoritmos utilizados en audio/radio. Por su parte las mencionadas instrucciones AVX le permiten a los procesadores AMD-FX poder desempeñar un mejor rendimiento en tareas multimedia como también modelado 3D dentro de lo más cotidiano y otros beneficios a nivel más profesional como procesado de señal, simulaciones científicas, análisis financiero, simulaciones científicas. Bloque Front-End: A nivel periférico, dentro de la arquitectura de Bulldozer tenemos el bloque Fron-End (muy similar al bloque Font-End que hemos visto en las arquitecturas gráficas). Este bloque compartido para cada uno de los módulos de Bulldozer es el responsable de impulsar las canalizaciones de procesamiento y

- 16. fue diseñado para asegurarse que siempre y todo el tiempo los núcleos de proceso estén constantemente alimentados de datos o información. Este bloque debido al diseño modular, ha sido rediseñado para poder trabajar con cada módulo (dual-core), además de asignar cada hilo de ejecución a cada uno de los núcleos. Los módulos Bulldozer pueden decodificar hasta 4 instrucciones por ciclo, esto comparado con las 3 instrucciones por ciclo que pueden decodificar los procesadores AMD Phenom II. Esto incrementa la cantidad de instrucciones que puede procesar Bulldozer por ciclo de reloj, lo que lo hace más eficiente en cuanto al cómputo de datos. Simultaneous MultiThreding AMD ha implementado en sus procesadores Bulldozer su propia tecnología SMT (Simultaneous MultiThreding), algo similar a la tecnología Hyper-Threding de Intel en sus principios básicos de simular más núcleos para el sistema que los disponibles físicamente. Bulldozer soporta 2 hilos de ejecución por núcleo, así en los modelos de cuatro núcleos, 8 serán los hilos de ejecución que administrará el procesador y 8 los núcleos que el sistema operativo podrá ver a nivel lógico. Todo esto de una manera mucho más “fuerte” y eficiente que la implementación de Intel y transparente para el sistema operativo y las aplicaciones, donde no se requerirá drivers para que el software reconozca el hardware multi-hilo como tal.

- 17. El hecho de ser un diseño modular la implementación de cada hilo de ejecución contará con su propia unidad de cálculo de enteros no teniendo que compartirla y disputarse los recursos con otras instancias (threads), con la consiguiente ganancia en la eficiencia de rendimiento que esto conlleva. Fuente. http://www.madboxpc.com/review-amd-fx-8150-black-edition-bulldozer/2/ “En la actualidad, AMD FX sigue el nuevo diseño de núcleos Piledriver, una evolución de Bulldozer que promete entregar — esta vez sí — el rendimiento propio de estas CPUs de alto rendimiento. “Vishera”, nombre en clave de la nueva plataforma, se compone de nuevas CPUs con hasta 8 núcleos Piledriver en dos o cuatro módulos, y está acompañada por las APU Kaveri, tanto para sistemas portátiles como desktop, con 2 o 4 núcleos Steamroller y chip gráfico basado en la nueva arquitectura GCN, propia de las GPUs de alto rendimiento AMD Radeon HD7700 y superiores, lo que significa un avance considerable con respecto a su predecesora proverbial, la todavía no lanzada plataforma Trinity, que también incluirá gráficos de la familia HD7000, basada en los núcleos Northern Islands (HD6000). Lo interesante de estas unidades aceleradas es que entrarán en el nuevo estándar HSA (Heterogeneous Systems Architecture) de AMD, que permite distribuir el trabajo de procesamiento general entre CPU y GPU de forma paralela automáticamente, como si se tratase de dos procesadores idénticos funcionando en el mismo sistema, lo que en teoría, y siempre que el software esté optimizado ayudaría a aumentar de un modo significativo el rendimiento de las APU. En el

- 18. tramo más bajo, posiblemente para sistemas económicos se encuentra las APU “Kabini”, con 2-4 núcleos Jaguar y gráficos GCN, aunque sin optimización HSA, como actualización de próxima generación de Brazos, la plataforma de gama baja de AMD. Vishera, Kaveri y Kabini no es lo único nuevo de los laboratorios de desarrollo de AMD; la compañía comprende el avance de las nuevas plataformas móviles, y por eso ha hecho un esfuerzo extra para acomodarse a la tendencia, produciendo las APU Tamesh ULP (Ultra Low Power), que también llegan este año (2013), y que será el rival de los nuevos procesadores Intel Medfield tanto para sistemas informáticos “Zero Noise” — HTPCs, Netbooks — como para tablets de consumo. 2013 se plantea como un año bastante interesante para la guerra de procesadores, con unos Ivy Bridge que compiten en el terreno del consumo y temperatura, Atoms que se centran en la autonomía y rendimiento gráfico, y las propuestas de AMD, encabezadas por una nueva generación de procesadores FX que prometen corregir errores del pasado.”4 APU Richland5 La segunda generación de APU (Accelerated Processing Unit)6 de AMD llegó el pasado mes de Mayo, aunque en un principio llegaron solamente para ordenadores portátiles y fabricantes OEM. Ahora AMD lanza la nueva plataforma Richland que ofrece diversas mejoras para disminuir su consumo y aumentar su rendimiento. La nueva plataforma de APU Richland para ordenadores portátiles estará formada en principio por cuatro modelos, A10-5750M, A8-5550M, A6-5350M y A4-5150M. Estas APU Richland consiguen mejorar el rendimiento de la anterior generación, la duración de la batería también aumenta, han sido pensadas para ser montadas en ultrathins, los gráficos de esta nueva generación de APU pertenecen a la serie AMD Radeon HD 8000. AMD ha incorporado varias características para mejora la experiencia de los usuarios. En primer lugar vamos a hablar de la función AMD Gesture Control, gracias a ella el usuario puede realizar gestos con las manos para controlar el 4 2013 es el año de AMD. Recuperado el 29 de marzo de 2013 http://www.taringa.net/posts/info/14395734/2013-es-el-ano-de-AMD.html 5 APU Richland: AMD anuncia la nueva generación de APUs 6 Un Accelerated processing unit en español Unidad de Procesamiento Acelerado o APU, dichos microprocesadores combinan una CPU multinúcleo, una GPU además de un bus de interconexión de alta velocidad que permite transferir información a mayores velocidades, debido a que se encuentran en el mismo chip el CPU la GPU y controlador de memoria entre otros, esto es posible gracias a la miniaturización de los chips actuales procesos de fabricación de entre 40 y 32 nm.

- 19. navegador, el reproductor multimedia y otras aplicaciones a una distancia máxima de 3 metros, esta tecnología es exclusiva de AMD, es decir, ningún fabricante dispone de esta función en estos momentos. Pasamos ahora a la función AMD Face Login, que como podemos deducir por su nombre, sirve para iniciar sesión o acceder a sitios webs mediante la identificación de los rasgos faciales. La función AMD Screen Mirror sirve para transmitir la imagen del PC a un televisor a través de DLNA. Para mejorar el entretenimiento multimedia incorpora las funciones AMD Quick Stream, AMD Steady Video y AMD Perfect Picture HD. Veamos las especificaciones de las primeras cuatro APU que AMD va a lanzar. Empezamos por la de menor rendimiento, la A4-5150M, esta APU cuenta con 2 núcleos que funcionan a una frecuencia base de 2,7 GHz, pudiendo aumentar hasta 3,3 GHz, cuenta con los gráficos integrados HD 8350G que tienen 128 Cores y funcionan a 514/720MHz (base, máxima) incorpora 1 MB de caché L2 y su TDP es de 35W. Comparativa de consumo de Richland y Trinity. La APU A6-5350M también incorpora 2 núcleos pero funcionan a 200 MHz más, los gráficos son los HD 8450G que incluyen 192 Cores funcionando a una frecuencia que va desde los 533 MHz a los 720 MHz, el TDP es de 35W y tiene 1 MB de caché L2. Los otros dos modelos, la A8-5550M y la A10-5750M, cuentan con 4 núcleos funcionando a una velocidad base de 2,1 GHz y 2,5 GHz, pudiendo alcanzar un máximo de 3,1 GHz y 3,5 GHz, respectivamente. La A8-5550M está equipada con los gráficos HD 8550G que tienen 256 Cores con unas frecuencias de 515/720 MHz y la A10-5750M cuenta con los gráficos HD 8650G que tienen 384 Cores y funcionan a 533/720 MHz, ambos cuentan con 4 MB de caché L2 y su TDP es de 35W.

- 20. Procesadores Intel 20137 El año es importante por la llegada de la nueva arquitectura Haswell, también conocidos como Intel Core de Cuarta Generación. Se esperan mejoras en el consumo y en las prestaciones de su tarjeta gráfica integrada. La siguiente es la lista de los procesadores aparecidos hasta la fecha: Familia Celeron Empezamos por los menos poderosos, los Celeron. En este caso estarán basados en Ivy Bridge, al igual que ocurre con los Core de Tercera Generación, pero con algunas de sus funcionalidades capadas. Como características comunes te encontraras que tienen 2 MB de cache de nivel tres y dos núcleos de su interior. Por supuesto no soportan Turbo Boost. Consumo normal Celeron G1610. Tienen una frecuencia de funcionamiento de 2.6 GHz. Su TDP, o consumo máximo teórico es de 55 Watios. Celeron G1620. Es 100 MHz más rápido que su hermano menor. Por lo demás comparten las mismas características. Bajo consumo Celeron G1610T. Se baja su frecuencia a 2.3 GHz. Su TDP se disminuye a 35 Watios. Familia Pentium Los Pentium son esos procesadores perfectos para ser usados en una oficina, ya que combinan bajo precio y prestaciones más que suficientes para ello. Al igual que ocurre con los anteriores están basados en Ivy Bridge y por lo tanto son parecidos a los Intel Core de Tercera Generación pero con varias características reducidas. Todos tienen en común 3 MB de cache de nivel tres y el doble núcleo. Por supuesto tampoco soportan Turbo Boost. Consumo normal Tienen todos un TDP de 55 Watios. 7 Sánchez Iglesias Ángel Luis. Procesadores Intel 2013 para PCs de escritorio. Guía de About.com. Consultado el 29 de marzo de 2013. http://computadoras.about.com/od/modelos/a/Procesadores-Intel-2013- Para-Pcs-De-Escritorio.htm

- 21. Pentium G2010. Tiene una frecuencia de funcionamiento de 2.8 GHz. Pentium G2020. Aumenta la frecuencia de funcionamiento a 2.9GHz. Pentium G2130. Llegamos a los 3.2 GHz. Por lo demás es igual que su hermano menor. Bajo consumo Pasamos a los 35 Watios de TDP. Pentium G2020T. Se baja la frecuencia de funcionamiento a 2.5GHz. Familia i3 Intel no ha querido dejar pasar la oportunidad de actualizar su gama media baja con un nuevo procesador i3 basado como no podía ser de otra forma en Ivy Bridge. i3-3210. 3.2 Ghz de frecuencia de funcionamiento. 3 Megas de cache de nivel tres. Dos núcleos con hyperthread. Futuros procesadores Haswell Se espera que vayan apareciendo a partir de Mayo. Familia i5 Empezamos con lo interesante. Tanto para los procesadores i5 como los i7 el fabricante nos va a traer su nueva arquitectura Haswell. Seguramente serán comercializados como Intel Core de Cuarta Generación. Vienen con un nuevo socket, con lo cual tendrás que adquirir al menos la placa base para disfrutar de ellos. A excepción del 4550T todos los demás son procesadores con cuatro núcleos, 6 MB de cache de nivel tres e incorporan la tarjeta gráfica integrada modelo HD 4600. Consumo normal Todos tienen 84 Watios de TDP. Core i5-4670K. Su frecuencia de funcionamiento es de 3.4GHz, pudiendo llegar a 3.8 GHz gracias a Turbo Boost. La frecuencia de la tarjeta de la tarjeta gráfica es de 1200 MHz. Puede usarse para overclocking. Core i5-4670. Igual que el anterior pero su capacidad de jugar con la frecuencia está más limitada.

- 22. Core i5-4570. Se baja la frecuencia base a 3.2GHz, siendo 3.6 GHz gracias a Turbo Boost. La frecuencia de la tarjeta gráfica es de 1150 MHZ. Core i5-4430. En este caso tenemos 3 GHz de frecuencia base, 3.2 gracias a Turbo Boost. La frecuencia de funcionamiento de la tarjeta es igual que el modelo anterior. Bajo consumo Estos tienen un consumo de 65 Watios Core i5-4430S. Tiene 2.7GHz de frecuencia base, pudiendo llegar a 3.2GHz. La frecuencia de su tarjeta integrada es de 1100 MHz. Core i5-4670S. Funciona a 3.1GHz, pudiendo llegar a 3.8 GHz. La frecuencia de la tarjeta es de 1200 MHz. Core i5-4570S. Funciona a 2.9GHz, alcanzando los 3.6 GHz. La frecuencia de la tarjeta es de 1150MHz. Ultra bajo consumo Core i5-4570T. Estamos ante un micro de 2.9GHz, que puede llegar a 3.6 GHz. 4MB de cache de nivel tres y dos núcleos con hyperthread. Su TDP es de 35 Watios. Core i5-4670T. Funciona a 2.3GHz, pudiendo llegar a 3.3 GHz en caso de usar el modo turbo. La frecuencia de la tarjeta 1200 y su TDP es de 45 Watios. Familia i7 Todos tienen 4 núcleos e hyperthread. 8 megas de cache de nivel tres. Consumo normal Todos tienen 84 Watios de TDP. Core i7-4770. Funciona a 3.4GHz de velocidad base y a 3.9GHz gracias al modo turbo. Frecuencia de la tarjeta 1200 MHz. Core i7-4770K. Funciona a 3.5GHz y 3.9 GHz en modo turbo. Pensado para hacer overclocking la frecuencia de la tarjeta es de 1250 MHz. Bajo consumo Core i7-4770S. 3.1GHz en modo normal y 3.9GHz en modo turbo. 65w de TDP. También tiene una tarjeta funcionando a 1200 MHz. Ultra bajo consumo

- 23. Todos vienen con la tarjeta a 1200MHz. Core i7-4765T. 2GHz en modo normal y 3 GHz en modo turbo. 35w de TDP Core i7-4770T. Pasamos a 2.5GHz en modo normal y a 3.7Ghz en modo turbo. 45w de TDP. Procesadores Intel® Core™ de cuarta generación con chipset Intel® Q87 (Anteriormente Shark Bay Desktop (Haswell + Lynx Point)) Los nuevos microprocesadores Intel Core de cuarta generación “Haswell” ofrecen arquitecturas CPU y GPU más refinadas, un rendimiento por ciclo algo superior, mejores características de overclock, tecnología HyperThreading más inteligente, nuevos y modernos juegos de instrucciones, y una arquitectura gráfica más sólida, compatible y optimizada para el cómputo acelerado por GPU (API OpenCL), características superiores a las presentes en los ahora “viejos pero aún efectivos” Core de tercera generación “Ivy Bridge”. Estos procesadores se fabrican con tecnología de procesamiento de 22 nm con transistores 3-D Tri-Gate. Con un total de 1.400 millones de transistores en una superficie de encapsulado de tan solo 177mm2 .Los desarrolladores también pueden utilizar la memoria del código de corrección de errores (ECC) cuando ciertos procesadores se usan con el chipset Intel® C226. Gráficos HD Intel® 4600: Entrega capacidades de medios y gráficos de alto rango para dispositivos de visualización de videos, gráficos en 2D y 3D y contenido interactivo. Extensiones vectoriales avanzadas Intel® 2: Acelera el desempeño informático de número entero y matriz para las aplicaciones de procesamiento de señales e imágenes. Nuevas instrucciones del estándar de encriptación avanzada Intel® (Intel® AES-NI): Compatible con la aceleración de hardware para la encriptación y desencriptación de datos. Intel® Flex E/S: Permite al usuario asignar de cuatro a seis puertos SATA de 6,0 Gbps, de seis a ocho puertos PCI Express* generación 2.0 y de cuatro a seis puertos USB 3.0, en base a las necesidades de configuración. Tecnología Intel® vPro™: Ofrece compatibilidad de hardware sin precedentes para funciones fundamentales de seguridad y administración. Plataforma basada en el procesador Intel® Core™ y el chipset Intel® Q87 para sistemas inteligentes. Puede consultar el datasheet en: http://www.intel.la/content/www/xl/es/intelligent-systems/shark-bay/core-q87- chipset-is-brief.html

- 24. Hoja de datos de la familia Core de cuarta generación para equipos de escritorio, Vol. 1: http://www.intel.la/content/www/xl/es/processors/core/4th-gen- core-family-desktop-vol-1-datasheet.html Hoja de datos de la familia Core de cuarta generación para equipos de escritorio, Vol. 2: http://www.intel.la/content/www/xl/es/processors/core/4th- gen-core-family-desktop-vol-2-datasheet.html Especificaciones Procesadores1 , 2 , 3 , 4 , 5 , 6 Número de procesador Código de pedido Velocidad de reloj de caché Alimentación Memoria Tecnologías del producto Procesador Intel® Core™ i7- 4770S CM8064601465504 Caché de 8M, hasta 3,90 GHz 65 W Canal doble DDR3/DDR3L 1600 @ 1,5 V Nuevas instrucciones de AES Intel® (Intel® AES- NI), Intel® AVX, tecnología Intel® Turbo Boost,

- 25. tecnología Intel® HT, tecnología Intel® vPro™ Procesador Intel® Core™ i7- 4770TE CM8064601538900 Caché de 8M, hasta 3,30 GHz 45 W Canal doble DDR3/DDR3L 1600 @ 1,5 V Intel AES-NI, Intel AVX, tecnología Intel Turbo Boost, tecnología Intel HT, tecnología Intel vPro Procesador Intel® Core™ i5- 4570S CM8064601465605 Caché de 6M, hasta 3,60 GHz 65 W Canal doble DDR3/DDR3L 1600 @ 1,5 V Intel AES-NI, Intel AVX, tecnología Intel Turbo Boost, tecnología Intel HT, tecnología Intel vPro Procesador Intel® Core™ i5- 4570TE CM8064601484301 Caché de 4M, hasta 3,30 GHz 35 W Canal doble DDR3/DDR3L 1600 @ 1,5 V Intel AES-NI, Intel AVX, tecnología Intel Turbo Boost, tecnología Intel HT, tecnología Intel vPro, ECC opcional Chipsets Producto Código de pedido Encapsulado Alimentación Características Chipset Intel® Q87 DH82Q87 FCBGA 708 4,1W De cuatro a seis puertos SATA (de dos a cuatro SATA de 6,0 Gbps); 14 puertos USB en total (de cuatro a seis USB 3.0); de seis a ocho puertos PCI Express* generación 2.0; compatibilidad con la tecnología

- 26. Intel® vPro™ Chipset Intel® C226 DH82C226 FCBGA 708 4,1W Compatible con ECC e Intel® AMT 9.0; de cuatro a seis puertos SATA de 6,0 Gbps; 14 puertos USB en total (de cuatro a seis USB 3.0); de seis a ocho puertos PCI Express*g generación 2.0 En el mercado de sobremesa se encuentran también series de cuatro y dos núcleos convencionales, todos dentro de las gamas Core i3 y Core i5, con variantes T y S con bajo consumo. El rendimiento de Haswell Las aplicaciones actuales no son capaces de aprovechar el potencial del nuevo microprocesador, pero aun así consigue resultados ligeramente superiores a los de Ivy Bridge. Futuras aplicaciones optimizadas para los nuevos juegos de instrucciones AVX 2.0 y FMA3 impulsaran el rendimiento del nuevo chip en hasta un 70%; factor que sumado a su mayor rendimiento en aplicaciones actuales, convierten a esta nueva generación de microprocesadores en una mejor elección que Ivy Bridge. El socket LGA 1150 Todas las mejoras introducidas en Haswell requieren de cambios físicos y eléctricos, introducidos por Intel en el nuevo socket LGA 1150 que estrenan estos nuevos microprocesadores. El nuevo socket LGA 1150 a diferencia de los anteriores y efímeros sockets LGA 1155 (Ivy Bridge y Sandy Bridge) y LGA 1156 (Nehalem), tendrá un largo tiempo de vigencia (hasta el 2016). Diagrama en bloques Este diagrama de bloque proporciona una descripción de las funciones, prestaciones y conectividad dentro de la plataforma de procesador Intel® indicada. Estos procesadores se basan en la microarquitectura de Intel® anteriormente

- 27. conocida como Haswell, fabricada en tecnología de procesamiento de 22 nm con transistores 3-D Tri-Gate. Esta plataforma brinda excelente CPU, gráficos, desempeño de medios, flexibilidad y mejor seguridad que los procesadores Intel® Core™ de tercera generación, lo que la hace ideal para una amplia gama de sistemas inteligentes. Los desarrolladores también pueden utilizar la memoria de ECC cuando ciertos procesadores se usan con el chipset Intel® C226. Nota: Luego de esta familia de cuarta generación, se pasa a la arquitectura "Skylake (Skymont)" de 14 y 10nm, en la que aparecerá la PCI Express 4.0 que permitirá un flojo de información a una velocidad de 100 Gbps a partir de fines de 2016. De los procesadores de 22nm se sabe que su performance se incrementará en un 37% y su consumo se reducirá más del 50%. Los 10nm del Skymont que es menos de la mitad de tamaño consumirán la mitad también. Otro dato interesante es que los actuales "Gulftown" de 32nm (entre ellos las ediciones extreme de i7) poseen 1170 millones de transistores. Los 22nm superarán los 2000 millones. Aparte de PCI Express 4.0, otra tecnología que está por cumplir una nueva versión es DDR, que a partir de 2012 tiene la versión 4. DDR4 corre a 2.133 y 2.667 MHz de forma estándar, y versiones especiales a los 3.200 MHz. Todo esto consumiendo menos energía ya que necesitarán 1.2 voltios (DDR3 1.5v)

- 28. HyperTransport8 HyperTransport (HT), también conocido como Lightning Data Transport (LDT) es una tecnología de comunicaciones bidireccional, que funciona tanto en serie como en paralelo, y que ofrece un gran ancho de banda en conexiones punto a punto de baja latencia. Se publicó el 2 de abril de 2001. Esta tecnología se aplica en la comunicación entre chips de un circuito integrado ofreciendo un enlace (ó bus) avanzado de alta velocidad y alto desempeño; es una conexión universal que está diseñada para reducir el número de buses dentro de un sistema, suministrando un enlace de alto rendimiento a las aplicaciones incorporadas y facilitando sistemas de multiprocesamiento altamente escalables. El HyperTransport Consortium es quien está llevando a cabo el desarrollo y promoción de la tecnología HyperTransport. Esta tecnología es ampliamente usada por las empresas AMD en procesadores x86 y chipsets; PMC-Sierra, Broadcom y Raza Microelectronics en microprocesadores; MIPS, NVIDIA, VIA Technologies y Silicon Integrated Systems en chipsets; HP, Sun Microsystems, IBM y Flextronics en servidores; Cray, Newisys, QLogic y XtremeData en sistemas informáticos de alto rendimiento, y Cisco Systems en routers. 8 HyperTransport. Recuperado el 29 de marzo de 2013. http://es.wikipedia.org/wiki/HyperTransport

- 29. Existen cuatro versiones de HyperTransport -- 1.x, 2.0, 3.0 y 3.1 -- que puede funcionar desde los 200MHz hasta 3.2GHz (mientras el bus PCI corre a 33 o 66 MHz). También soporta tecnología DDR (o Double Data Rate), lo cual permite alcanzar un máximo de 5200 MT/s (2600MHz hacia cada dirección: entrada y salida) funcionando a su máxima velocidad (2.6GHz). Soporta conexiones auto-negociadas para determinar la velocidad. Su velocidad de transferencia máxima, utilizando líneas de 32 bits, tiene por cada uno de sus 2

- 30. buses un total de 20.8 GB/s (2.6GHz * (32bits / 8)), lo que supone la suma de 41.6 GB/s en ambas direcciones, superando con creces cualquier otro estándar. Se pueden mezclar también enlaces de varios anchos en una sola aplicación (por ejemplo 2x8 en vez de 1x16). Esto permite una velocidad de interconexión mayor entre la memoria principal y la CPU y una menor entre los periféricos que lo precisen. Además esta tecnología tiene mucho menos latencia que otras soluciones. HyperTransport está basada en paquetes. Cada uno de ellos consiste en un conjunto de palabras de 32 bits independientemente del ancho físico de la conexión. La primera palabra de un paquete es siempre una palabra de comando. Si un paquete contiene una dirección los últimos 8 bits de la palabra de comando estarán enlazados con la siguiente palabra de 32 bits para formar una dirección de 40 bits. Además se permite anteponer otra palabra de control de 32 bits cuando se necesite una dirección de 64 bits. Las restantes palabras de 32 bits en un paquete formarán la información útil. Las transferencias, independientemente de su longitud actual, estarán formadas siempre por múltiplos de 32 bits. Los paquetes de HyperTransport entran en segmentos conocidos como tiempos bit. El número de tiempos bit necesarios depende del ancho de la interconexión. HyperTransport puede usarse para generar mensajes de gestión de sistemas, señales de interrupciones, expedir sondas a dispositivos adyacentes o procesadores y E/S en general y hacer transacciones de datos. Normalmente se pueden usar dos tipos diferentes de comandos de escritura: avisados y no- avisados. Las escrituras avisadas no precisan una respuesta del destino. Son usadas primordialmente para dispositivos con un gran ancho de banda como tráfico a Uniform Memory Access o transferencias de Acceso directo a memoria. Las escrituras no-avisadas precisan una respuesta del tipo "destino hecho". La lectura también puede provocar que el receptor genere una respuesta. Aplicaciones El desarrollo de HyperTransport se hizo sobre la base de querer eliminar el Front Side Bus (FSB). No fue hasta la versión 3.0 cuando varios fabricantes de chipsets

- 31. decidieron utilizar HyperTransport para sustituir el FSB con excelentes resultados. Ésta ha sido su implementación más famosa. También ha dado grandes resultados en otras implantaciones, tales como interconexiones entre microprocesadores MIPS, servidores, sistemas informáticos de alto rendimiento, y en routers y switches. Implementaciones AMD AMD64 y CPUs basadas en Direct Connect Architecture. SiByte CPUs MIPS de Broadcom CPUs MIPS de PMC-Sierra RM9000X2 ht_tunnel del proyecto OpenCores (licencia MPL) ATI Radeon Xpress 200 para el procesador AMD Chipsets NVIDIA nForce nForce Professional MCPs (Media and Communication Processor) Serie nForce 4 Serie nForce 500 Serie nForce 600 Serie nForce 700 Controlador de E/S HyperTransport ServerWorks (ahora Broadcom) HT- 2000 El Puente norte del IBM PowerPC G5 CPC925 y CPC945 Los procesadores multihilo Raza HyperTransport e HyperThreading El uso de las mismas siglas para su denominación (HT) ha llevado a generar confusiones entre el público. No se deben confundir ya que ambas tecnologías son completamente distintas. Muchas veces para referirse al HyperTransport también se utilizan las siglas HTT. Especificaciones de frecuencias de HyperTransport

- 32. HyperThreading9 La tecnología HyperThreading tiene grandes capacidades de procesamiento y rapidez. Algunas de sus ventajas son: mejora el apoyo de código “multi-hilos”, que permite ejecutar múltiples hilos simultáneamente, mejora de la reacción y el tiempo de respuesta. De acuerdo con el primer informe de Intel, los Pentium 4 que incorporan esta tecnología tienen un rendimiento entre un 15% y un 30% superior al de los procesadores sin HyperThreading, y utilizan sólo un 5% más de recursos. 9 HyperThreading. Recuperado el 29 de marzo de 2013. http://es.wikipedia.org/wiki/HyperThreading

- 33. La tecnología HyperThreading tiene grandes capacidades de procesamiento y rapidez. Algunas de sus ventajas son: mejora el apoyo de código “multi-hilos”, que permite ejecutar múltiples hilos simultáneamente, mejora de la reacción y el tiempo de respuesta. De acuerdo con el primer informe de Intel, los Pentium 4 que incorporan esta tecnología tienen un rendimiento entre un 15% y un 30% superior al de los procesadores sin HyperThreading, y utilizan sólo un 5% más de recursos. Criticas ARM10 criticó la tecnología SMP por no ser eficiente energéticamente. Intel retiró temporalmente el hyperthreading de sus nuevos diseños pero los últimos procesadores i3 e i7 la incorporan de nuevo. Familias de procesadores Intel que incorporan la tecnología Hyper Threading: Intel Pentium 4 Intel Pentium 4 Extreme Edition Intel Pentium D Extreme Edition Intel Pentium G400 (Algunos modelos) Intel Pentium G600 (Algunos modelos) Intel Celeron G400 Intel Celeron C800 Intel Core i3 Intel Core i3 Sandy Bridge Intel Core i5 Intel Core i5 Sandy Bridge Intel Core i5 Ivy Bridge Intel Core i7 Intel Core i7 Sandy Bridge Intel Core i7 Ivy Bridge Intel Core i7 Extreme Edition Intel Atom N270 Intel Atom N450 Intel Atom N550 Intel Atom N570 Intel Xeon MP Intel Xeon E3 10 ARM es una arquitectura RISC (Reduced Instruction Set Computer=Ordenador con Conjunto de Instrucciones Reducidas) de 32 bits desarrollada por ARM Holdings. Se llamó Advanced RISC Machine, y anteriormente Acorn RISC Machine. La arquitectura ARM es el conjunto de instrucciones de 32 bits más ampliamente utilizado en unidades producidas. Fuente. ARM Cores Climb Into 3G Territory. Mark Hachman, 2002.

- 34. Intel Xeon E5 Se pueden consultar todos los procesadores con HT en el enlace. http://ark.intel.com/search/advanced/?s=t&HyperThreading=true Multiprocesamiento simétrico11 En computación, SMP (del inglés Symmetric Multi-Processing, en español "multiproceso simétrico") es un tipo de arquitectura de computadores en la que dos o más unidades de procesamiento comparten una única memoria central. La arquitectura SMP (también llamada UMA, del inglés Uniform Memory Access, en español "acceso uniforme a memoria") se caracteriza por el hecho de que varias unidades de procesamiento comparten el acceso a la memoria, compitiendo en igualdad de condiciones por dicho acceso, de ahí la denominación "simétrico". Los sistemas SMP permiten que cualquier procesador trabaje en cualquier tarea sin importar su localización en memoria; con un propicio soporte del sistema operativo, estos sistemas pueden mover fácilmente tareas entre los procesadores para garantizar eficientemente el trabajo. Una computadora SMP se compone de microprocesadores independientes que se comunican con la memoria a través de un bus compartido. Dicho bus es un recurso de uso común. Por tanto, debe ser arbitrado para que solamente un microprocesador lo use en cada instante de tiempo. Si las computadoras con un único microprocesador tienden a gastar considerable tiempo esperando a que lleguen los datos desde la memoria, SMP empeora esta situación, ya que hay varios parados en espera de datos. 11 Multiprocesamiento simétrico. Recuperado el 29 de marzo de 2013. http://es.wikipedia.org/wiki/Multiprocesamiento_sim%C3%A9trico

- 35. Conceptos relacionados Arquitectura NUMA “NUMA (Non-Uniform Memory Access, "acceso a memoria no uniforme") es un diseño de memoria utilizado en multiprocesamiento donde la memoria se accede en posiciones relativas de otro proceso o memoria compartida entre procesos. Bajo NUMA, un procesador puede acceder a su propia memoria local de forma más rápida que a la memoria no local (memoria local de otro procesador o memoria compartida entre procesadores). Limitar el número de accesos a memoria es la clave de un alto rendimiento en un ordenador moderno. Para los procesadores esto significa el incremento de alta velocidad de la memoria caché y el uso de algoritmos más sofisticados para evitar los errores de caché. Aunque el drástico aumento del tamaño de los sistemas operativos y las aplicaciones que se ejecutan en ellos han abrumado las mejoras del procesamiento de la caché. Los sistemas de multiprocesamiento12 hacen que 12 Multiprocesamiento o multiproceso es tradicionalmente conocido como el uso de múltiples procesos concurrentes en un sistema en lugar de un único proceso en un instante determinado. Como la multitarea que permite a múltiples procesos compartir una única CPU, múltiples CPUs pueden ser utilizados para ejecutar múltiples hilos dentro de un único proceso. El multiproceso para tareas generales es bastante difícil de conseguir debido a que puede haber varios programas manejando datos internos (conocido como estado o contexto) a la vez. Los programas típicamente se escriben asumiendo que sus datos son incorruptibles. Sin embargo, si otra copia del programa se ejecuta en otro procesador, las dos copias pueden interferir entre sí intentando ambas leer o escribir su estado al mismo tiempo. Para evitar este problema se usa una variedad de técnicas de programación incluyendo semáforos y

- 36. el problema sea peor. Ahora el sistema debe bloquear varios procesadores a la vez, porque solo un procesador puede acceder a la memoria a la vez. NUMA intenta resolver este problema ofreciendo memoria distribuida para cada procesador, evitando así que afecte al rendimiento del sistema cuando varios procesadores intentan acceder a la misma memoria. Para los problemas de la propagación de datos (comunes en servidores y aplicaciones similares), NUMA puede mejorar el rendimiento utilizando una única memoria compartida por un factor de aproximadamente el número de procesadores (o separando bancos de memoria).”13 “Multiproceso simétrico, una de las formas más fáciles y baratas de aumentar el rendimiento del hardware es poner más de una CPU en la placa. Esto se puede realizar haciendo que CPUs diferentes tengan trabajos diferentes (multiproceso asimétrico) o haciendo que todos se ejecuten en paralelo, realizando el mismo trabajo (multiproceso simétrico o SMP). El hacer multiproceso asimétrico requiere un conocimiento especializado sobre las tareas que la computadora debe ejecutar, que no es fácilmente discernible en un sistema operativo de propósito general como Linux. En cambio el multiproceso simétrico es relativamente fácil de implementar. En un entorno de multiproceso simétrico, las CPU comparten la misma memoria, y como resultado, el código que corre en una CPU puede afectar a la memoria usada por otra. No se puede estar seguro de que una variable que se ha otras comprobaciones y bloqueos que permiten a una sola copia del programa cambiar de forma exclusiva ciertos valores. Recuperado el 29 de marzo de 2013. http://es.wikipedia.org/wiki/Multiprocesamiento 13 NUMA. Recuperado el 29 de marzo de 2013. http://es.wikipedia.org/wiki/NUMA

- 37. establecido a un cierto valor en la línea anterior todavía tenga el mismo valor; la otra CPU puede modificar el valor de la variable. No es posible programar algo de esta manera. En la figura mostrada, sobre el tema del HSA, busca unificar el espacio de desarrollo de la CPU y la GPU, en la que ambas se puedan programar como si fuese una sola entidad a ojos del programador, esta transición la empezó AMD en la arquitectura GCN al hacer que soportase memoria virtual y fuese compatible con el direccionamiento de memoria de la arquitectura x86 con tal de unificar el acceso a la memoria desde un mismo elemento en un futuro, por el momento se tiene el espacio de direcciones unificado pero no se tiene el acceso a la memoria unificado y precisamente, el acceso a la memoria unificado es la base para el HSA completo. Mirando la última APU de AMD en el mercado, conocida como Kabini, se observa como esta utiliza arquitectura Jaguar en la CPU y arquitectura GCN en su GPU (como las APU/SoC de PS4 y Xbox One), por lo que el futuro Kaveri de AMD soportará HSA completo, pero AMD no ha dado información de la arquitectura del mismo. Fuente de consulta. http://josepjroca.wordpress.com/2013/07/01/true-lies/ En el caso de la programación de procesos esto no suele ser un problema, porque un proceso normalmente sólo se ejecutará en una CPU a la vez. El núcleo, sin embargo, podría ser llamado por diferentes procesos ejecutándose en CPUs diferentes. En la versión 2.0.x del núcleo de Linux, esto no es un problema porque el núcleo entero está en un gran “spinlock”. Esto significa que si una CPU está dentro del núcleo y otra CPU quiere entrar en él, por ejemplo por una llamada al sistema,

- 38. tiene que esperar hasta que la primera CPU haya acabado. Esto es lo que hace el SMP en Linux; es seguro, pero ineficiente.”14 Latencia15 En redes informáticas de datos se denomina latencia a la suma de retardos temporales dentro de una red. Un retardo es producido por la demora en la propagación y transmisión de paquetes dentro de la red. Otros factores que influyen en la latencia de una red son: El tamaño de los paquetes transmitidos. El tamaño de los buffers dentro de los equipos de conectividad. Ellos pueden producir un Retardo Medio de Encolado. Hay latencia en tecnologías de uso musical, como los transformadores de mp3 a vinilos analógicos. Siempre el traspaso de información de un mecanismo a otro va a sufrir este retardo, que normalmente está estimado en milisegundos (1/1,000 s) en algunos casos pequeño, en otro más notorio. La latencia en el sentido del audio digital está directamente relacionada con la tarjeta de audio, esto se debe a que dicha tarjeta no es compatible con ASIO (Audio Stream Input Output). Un punto muy importante es que siempre va a haber cierta latencia, aun cuando se hable de latencia cero, la cuestión es que esta es imperceptible (3 ms aprox.) En general se refiere al tiempo que dura en llegar una acción desde su punto de inicio hasta su "punto de fuga", es decir cuando la acción se consuma. Se denominan latencias de una memoria RAM a los diferentes retardos producidos en el acceso a los distintos componentes de esta última. Estos retardos influyen en el tiempo de acceso de la memoria por parte de la CPU, el cual se mide en nanosegundos (10-9 s). Resulta de particular interés en el mundo del overclocking el poder ajustar estos valores de manera de obtener el menor tiempo de acceso posible. Estructura física de la memoria La memoria está compuesta por un determinado número de celdas, capaces de almacenar un dato o una instrucción y colocadas en forma de tablero de ajedrez. En lugar de tener 64 posibles posiciones donde colocar piezas, tienen n 14 Multiprocesamiento simétrico. Recuperado el 29 de marzo de 2013. http://es.wikipedia.org/wiki/Multiprocesamiento_sim%C3%A9trico 15 Latencia. Recuperado el 29 de marzo de 2013. http://es.wikipedia.org/wiki/Latencia

- 39. posiciones. No solo existe un "tablero" sino que existen varios, de esta forma la estructura queda en forma de tablero de ajedrez tridimensional. Acceso a memoria Cuando se desea acceder a la memoria, es imprescindible indicar el número de tablero, el número de fila dentro del tablero, y el número de columna o celda dentro de esa fila, en ese orden. El tiempo que tarda la memoria en colocarse en la posición necesaria es relativamente pequeño, sin embargo son tantos los datos e instrucciones que se almacenan en la memoria, que al final el proceso puede llegar a hacerse lento. Debido al que se van a leer/escribir muchas cosas de/en la memoria, se necesita un sistema que lea muchas celdas al mismo tiempo, sin transportar los datos de dichas celdas y a continuación, transportar todos los datos a la vez (dato o instrucción ya que es lo único que se almacena en la memoria). Este sistema de leer muchas celdas y después transportar es conocido como bus a ráfagas o burst. Si por cada celda que se leyese, el dato/instrucción se transportara a su destino, la lectura/escritura de memoria sería un proceso demasiado lento. Tipos de latencia Existen varios tipos de latencias en las memorias, sin embargo, las más importantes son: CAS: indica el tiempo que tarda la memoria en colocarse sobre una columna o celda. RAS: indica el tiempo que tarda la memoria en colocarse sobre una fila. ACTIVE: indica el tiempo que tarda la memoria en activar un tablero.

- 40. PRECHARGE: indica el tiempo que tarda la memoria en desactivar un tablero. Lectura o escritura de memoria El proceso a seguir cuando se desea leer o escribir en la memoria será el siguiente: Mandar una señal para activar el tablero y esperar a que termine el tiempo de activación (latencia ACTIVE). Mandar una señal para saber cuál es la fila en la que se debe posicionar y esperar a su latencia (latencia RAS). Mandar una señal para saber cuál es la columna o celda donde se debe posicionar y esperar (latencia CAS). Tiempo de espera El tiempo que tarda la memoria en proporcionar el dato, es la suma de las tres latencias: ACTIVE, RAS y CAS. Como se comenta anteriormente, antes de enviar el dato/instrucción a donde deba ir, se deben leer varias celdas de memoria, por lo tanto hay que pasar de una celda a otra, e ir esperando su correspondiente latencia CAS. Si cada tablero tiene, por ejemplo 64 celdas, y se van a leer 20 posiciones, las latencias totales a esperar son: 1 X ACTIVE (ya que se leen menos de 64 celdas, que son las que tiene el tablero completo) 3 X RAS (ya que cada fila tiene 8 posiciones) 20 X CAS (ya que se van a leer 20 celdas) La latencia más importante, como queda patente, es la latencia CAS, y cuanto menor sea esta, mejor rendimiento tendrá el ordenador en general. Tiempo real Sea una placa base con Front Side Bus16 o FSB a 200 MHz. El tiempo de cada ciclo de reloj es: F = 1 / T --> 200 * 106 = 1 / T --> 16 El front-side bus, también conocido por su acrónimo FSB (del inglés literalmente "bus de la parte frontal"), es el tipo de bus usado como bus principal en algunos de los antiguos microprocesadores de la marca Intel para hablar con el circuito integrado auxiliar o chipset. Ese bus incluye señales de datos, direcciones y control, así como señales de reloj que sincronizan su funcionamiento. En los nuevos procesadores de Intel, desde Nehalem, y hace tiempo en los de AMD se usan otros tipos de buses como el Intel QuickPath Interconnect y el HyperTransport respectivamente. Fuente Front-side bus. Recuperado el 29 de marzo de 2013. http://es.wikipedia.org/wiki/Front_Side_Bus

- 41. T = 1 / 200 * 106 --> T = 5 * 10-9 s = 5ns= 5 nanosegundos NOTA: las antiguas memorias RAM que empleaban los Pentium I eran de 70 ns, las EDO que eran las mismas un poco evolucionadas eran de 60 ns, así se puede calcular bastante fácilmente el fsb de aquellos sistemas. Las primeras SDRAM que aparecieron, las PC 100, eran de 10 ns, evidentemente el fsb de aquellos sistemas era de 100 MHz. En función de la calidad de las memorias, sus latencias serán mejores o peores. En la imagen se ve que la memoria tarda 12.5 ns en hacer el CAS, si se cogen 3 ciclos (latencia CAS 3) sobran 2.5 ns 2.5 en 15 es mucho el 16.6%, y más aun teniendo en cuenta que se hacen muchísimos accesos a memoria, por lo tanto, cuanto más tiempo se ahorre mejor. Al hacer uso de la memoria DDR, se puede emplear tanto el flanco de subida como el de bajada para terminar la latencia, de modo que empleando CAS 2.5 este ejemplo sería óptimo.

- 42. Latencias vs FSB (caso práctico) La diferencia de latencia es algo muy apreciable (en especial la latencia CAS) a la hora de medir el rendimiento del ordenador, ya que cuando se accede a memoria tanto para leer como para escribir se tiene que esperar por ella. Por cada celda del tablero que se lea, hay que esperar la latencia CAS, por cada fila completa al RAS, y por cada tablero diferente las ACTIVE y PRECHARGE (a veces se solapan). Se lee/escribe por ráfagas, pero en cada ráfaga se espera ‘x’ veces a CAS, ‘y’ veces RAS, siendo X = Y2 , ACTIVE, PRECHARGE, etc. Por otra parte cuanto más alto sea el FSB, más rendimiento se obtiene. Aunque es una verdad a medias. Las latencias son inversamente proporcionales a la velocidad del bus FSB/HTT, es decir, cuanto mayor FSB maneje el sistema, peor latencia manejará y viceversa. En la figura se observan dos sistemas: uno con un FSB de 100 MHz (izquierda) y otro, con un FSB de 200 MHz (derecha), al tener el doble de frecuencia tenemos que en el mismo tiempo se hacen el doble de ciclos, de ahí que a la derecha estén las “ondas” mucho más comprimidas. En ambos casos se emplea la misma memoria, que tarda una tiempo en hacer el acceso CAS. Este tiempo está marcado con una línea verde. La escala de tiempo en ambos casos es exactamente la misma, así que la línea verde será en ambos casos exactamente igual. Para el sistema de la izquierda, se puede ver que el CAS de la memoria es de casi 2 ciclos, para redondear, hay que redondear hacia arriba para darle tiempo a que

- 43. termine, sobrará un poco, sin embargo, para el caso de la derecha, el CAS sería de 3. En el último dibujo se ve que en la parte de la izquierda se pierde un poco de tiempo desde que se termina el CAS hasta que termina su latencia. Se ve el tiempo desperdiciado abajo a la derecha en color azul claro. Lo mismo pasa en el sistema del dibujo de la derecha. Pero en este caso es más tiempo (La escala temporal, eje de las abscisas, es el mismo en ambos casos, por lo tanto el tiempo es mayor a la derecha). En principio se podría pensar que aunque se pierda un poco más en un lado que en el otro, como el fsb es bastante superior en un lado que en el otro, seguro que es más rápido aun perdiendo un poco de tiempo en el CAS. A continuación se demuestra que esto no es cierto en todos los casos: Un sistema a 133 MHz y otro a 200 MHz, y empleando la misma, exactamente la misma memoria en ambos casos. El tiempo que tarda en ejecutarse un ciclo: 1/133 * 106 = 7.5 * 10-9 = 7.5 ns 1/200 * 106 = 6 * 10-9 = 6 ns Un ciclo en el sistema con bus a 200 MHz tarda 6 nanosegundos en ejecutarse y 7.5 nanosegundos en el sistema con bus a 133 MHz. Suponiendo que la memoria funciona en ambos sistemas con las siguientes latencias: Sistema 133 MHz --> 2 – 2 – 2 – 5 --> CAS, RAS, PRECHARGE y ACTIVE Sistema 200 MHz --> 3 – 2 – 2 – 5 --> CAS, RAS, PRECHARGE y ACTIVE Los tiempos que se tardaría en cada caso serían los siguientes: Sistema 133 MHz (2 * 7.5) + (2 * 7.5) + (2 * 7.5) + (5 * 7.5) = 15 + 15 + 15 + 37.5 = 82.5 ns

- 44. Sistema 200 MHz (3 * 6) + (2 * 6) + (2 * 6) + (5 * 6) = 18 + 12 + 12 + 30 = 72 ns Hasta aquí parecería que salen mal las cuentas ya que el sistema con bus a 200 MHz tarda menos tiempo, 72 ns frente a 82.5 ns Sin embargo, suponiendo que el tablero de la memoria es de 100 filas por 100 columnas las cosas cambian. Hay que recordar que la latencia CAS se ejecuta tantas veces como columnas haya, en este caso, 100 veces por cada vez que se ejecuta cambio de fila (RAS), por lo tanto, el cálculo justo, suponiendo que hay que leer en una ráfaga justo una fila entera quedaría de la siguiente manera: Sistema 133 MHz [100 * (2 * 7.5)] + (2 * 7.5) + (2 * 7.5) + (5 * 7.5) = (15 * 100) + 15 + 15 + 37.5 = 1500 ns + 67.5 ns = 1567.5 ns Sistema 200 MHz [100 * (3 * 6)] + (2 * 6) + (2 * 6) + (5 * 6) = (18 * 100) + 12 + 12 + 30 = 1800 ns + 54 ns = 1854 ns Este sería un caso extremo, que justo haya que leer una fila entera y no hubiera que hacer ni un solo salto de fila (RAS) ni cambios de tablero. Aunque aun así podría seguir siendo óptimo el caso del sistema con bus a 133. Con ese cálculo queda clara la importancia de la latencia CAS con respecto a las demás, y la importancia de las latencias con respecto al bus FSB/HTT. Front-side bus El front-side bus, también conocido por su acrónimo FSB (del inglés literalmente "bus de la parte frontal"), es el tipo de bus usado como bus principal en algunos de los antiguos microprocesadores de la marca Intel para hablar con el circuito integrado auxiliar o chipset. Ese bus incluye señales de datos, direcciones y control, así como señales de reloj que sincronizan su funcionamiento. En los nuevos procesadores de Intel, desde Nehalem, y hace tiempo en los de AMD se usan otros tipos de buses como el Intel QuickPath Interconnect y el HyperTransport respectivamente. Velocidad de componentes relacionados La frecuencia de trabajo del microprocesador se obtiene como resultado de multiplicar la Chancla de reloj del FSB (en megahercios, no en MT/s) por un factor multiplicador. Este factor multiplicador, así como la frecuencia pasada la media

- 45. noche de reloj del FSB pueden alterarse a través de la configuración de la placa base, generalmente a través de la BIOS, permitiendo así el overclocking. El ancho de banda del FSB depende de su tamaño de palabra (si es de 16, 32 o 64 bits), su frecuencia de reloj medida en megahercios y el número de transferencias que realiza por ciclo de reloj. Por ejemplo, un FSB de 32 bits de ancho (4 bytes), funcionando a 100 MHz y que realice 4 transferencias por cada ciclo, ofrece un máximo teórico de 1600 megabytes por segundo. Dando así al bus una velocidad de 1.6Ghz p/s esto hace que el bus que va al Disco Duro sea unas 32 veces más rápido e incluso 64. Por otra parte si se usa la tecnología Quad Data Rate, si el bus funciona a 100 MHz de señal de reloj, en cada ciclo de reloj hay cuatro transferencias de datos. Se dice entonces que el bus funciona a 400 MT/s, y su ancho de banda se expresa mediante la siguiente fórmula: 4 bytes x 100 MHz x 4 = 1600 MB/s Back-side bus Algunas computadoras tienen una memoria caché L2 o L3 externa a la propia CPU conectados mediante un back side bus (literalmente bus trasero o bus de la parte de atrás). El acceso a la memoria caché, conectada a este bus, es más rápido que el acceso a la memoria de acceso aleatorio por el FSB. En la actualidad, la caché L2, ha sido directamente incluida en el chip del microprocesador, junto con la caché L1. Historia y futuro El FSB empezó a formar parte de la arquitectura de computadoras estándar desde que las aplicaciones requieren más memoria de la que el procesador podría retener. Los más modernos FSB se utilizan a modo de conexión exclusiva principal entre la unidad central de procesamiento y el circuito integrado auxiliar. Éste (generalmente compuesto por el trabajo en conjunto del puente norte o northbridge y el puente sur o southbridge) es el encargado de interconectar el resto de buses del sistema. Los buses como PCI, PCI Express, y buses de memoria se comunican con el chipset para permitir el correcto flujo de datos entre los diferentes dispositivos. Generalmente estos buses secundarios funcionan a una velocidad derivada de la velocidad del FSB. Pese a la solución que dio al problema, siempre se ha pensado en que el FSB debería ser una tecnología con tendencia a desaparecer. Empresas como AMD

- 46. siempre han criticado el FSB, ya que limita mucho las capacidades reales de un sistema generando mucha latencia y un tiempo de respuesta mayor, creando un auténtico cuello de botella para el resto de dispositivos. No fue hasta 2001 y la aparición de la tecnología HyperTransport cuando se pudo diseñar una tecnología capaz de reemplazar el uso del FSB. Actualmente empresas fabricantes de chipsets como NVIDIA, Silicon Integrated Systems o VIA Technologies, ya han comenzado a eliminar el uso del FSB sustituyéndolo con la versión 3.0 de HyperTransport.