Que es el TLB

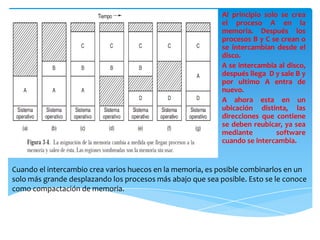

- 1. Al principio solo se crea el proceso A en la memoria. Después los procesos B y C se crean o se intercambian desde el disco. A se intercambia al disco, después llega D y sale B y por ultimo A entra de nuevo. A ahora esta en un ubicación distinta, las direcciones que contiene se deben reubicar, ya sea mediante software cuando se intercambia. Cuando el intercambio crea varios huecos en la memoria, es posible combinarlos en un solo más grande desplazando los procesos más abajo que sea posible. Esto se le conoce como compactación de memoria.

- 2. * TLB : Memoria asociativa, se encuentra en la MMU, consiste en un numero de entradas, ocho en este ejemplo, pero rara veces más de 64. * Cada entrada contiene información acerca de una página, incluyendo el número de página virtual, un bit que se establece cuando se modifica la página, el código de protección (permisos de lectura/escritura/ ejecución) y el marco de página físico en el que se encuentra la página. * Estos campos tienen una correspondencia de uno a uno con los campos en la tabla de páginas, excepto por el número de página virtual, que no se necesita en la tabla de páginas. * Otro bit indica si la entrada es válida (es decir, si está en uso) o no.

- 3. Es un caché de CPU que emplea el hardware de administración de memoria MMU para mejorar la velocidad de traducción de direcciones virtuales. Contiene partes de la tabla de paginación, es decir, relaciones virtuales y reales. Posee un numero fijo de entradas y se utiliza para obtener la traducción rápida de direcciones, si no existe una entrada buscada , se deberá revisar la tabla de paginación y tardará varios ciclos más, sobre toda la página que contiene la dirección buscada no está en memoria primaria.

- 5. Cuando se accesa una página cuya traducción se encuentra en la TLB, el sobrecosto es bajísimo. En cambio si la traducción no se encuentra en la TLB, sólo entonces se visitan el directorio y la tabla de páginas en la memoria real, con un sobrecosto de 2 accesos adicionales a la memoria. La traducción de esta página se coloca en la TLB para que los futuros accesos a esta página sean eficientes. Sin embargo, eventualmente será necesario suprimir una traducción previamente existente en la TLB, debido a su taman o limitado. Empíricamente se ha determinado que más del 99% de los accesos a memoria corresponde a páginas cuya traducción y atributos se encuentran en la TLB. Una restricción usual es que la TLB mantiene sólo la traducción de páginas pertenecientes al proceso en ejecución. Durante un cambio de contexto es necesario invalidar la TLB, para que no se encuentren en la TLB traducciones que corresponden erróneamente al proceso anterior. Este es un costo escondido del cambio de contexto: el proceso que recibe el procesador encuentra la TLB vacía, la que se irá poblando a medida que el proceso accesa sus páginas virtuales. Para cargar 64 filas de la TLB se habrán requerido 128 accesos