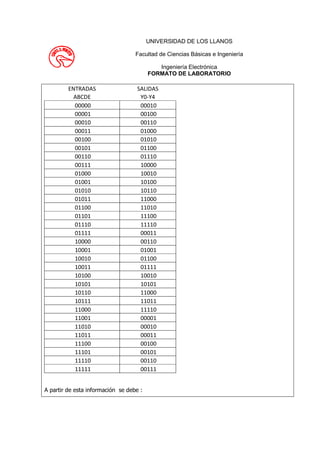

Este documento presenta el formato de laboratorio para el curso Circuitos Digitales I de Ingeniería Electrónica. Los estudiantes aprenderán a usar herramientas de diseño esquemático como Xilinx para describir el comportamiento de sistemas digitales. Deberán desarrollar un circuito que implemente ciertas funciones lógicas usando compuertas básicas y verificarlo generando trenes de pulsos. También deberán mapear la función a puertos usando VHDL. El trabajo deberá entregarse antes del 4 de mar