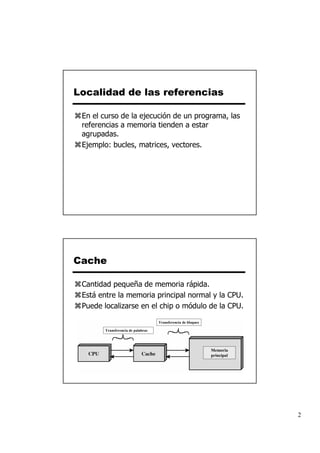

La memoria caché es una pequeña cantidad de memoria rápida ubicada entre la CPU y la memoria principal. Cuando la CPU solicita datos, primero revisa la caché. Si los datos están en la caché, se obtienen rápidamente de allí. De lo contrario, se copian bloques completos de datos de la memoria principal a la caché. La caché luego entrega los datos solicitados a la CPU mientras almacena el bloque completo para posibles referencias futuras.