Incrustar presentación

Descargar para leer sin conexión

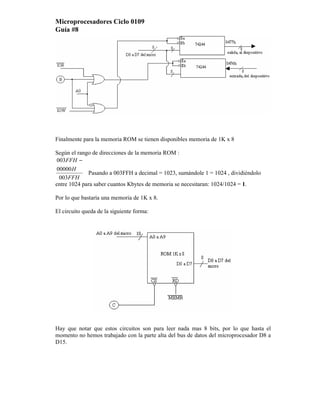

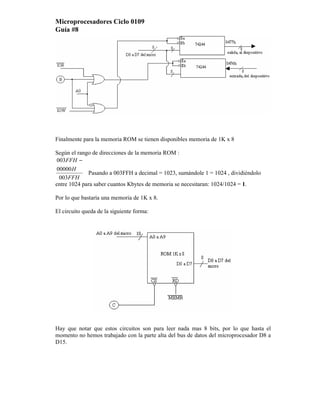

Este documento describe cómo conectar dispositivos de memoria y entrada/salida a un microprocesador. Explica los tipos principales de memoria RAM y ROM, sus terminales y cómo decodificar las direcciones de memoria para asignar rangos específicos a cada dispositivo. Luego, diseña circuitos decodificadores para asignar RAM de 8KB a direcciones FFFFFh-FE000h, E/S de 8 bits a 00477h-00476h y ROM de 1KB a 003FFh-00000h.