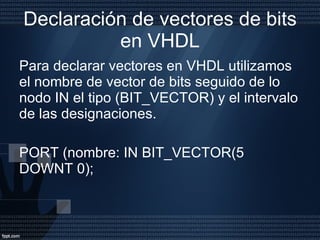

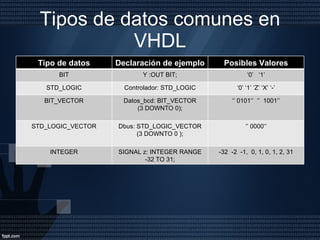

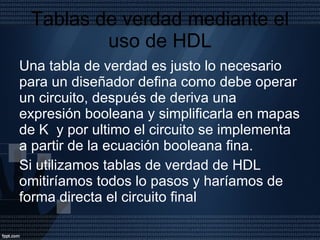

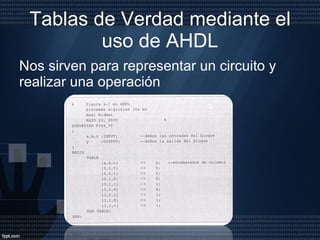

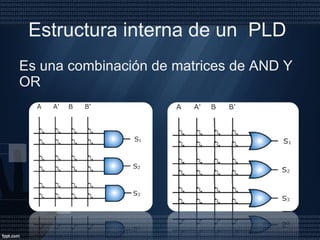

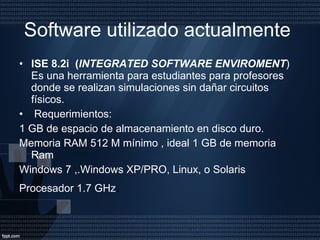

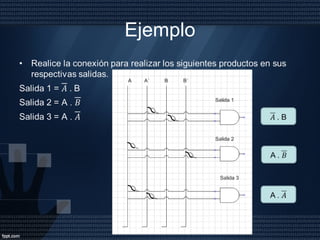

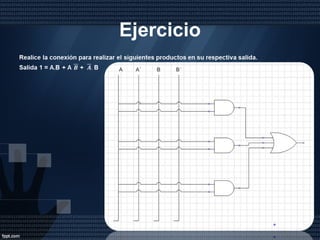

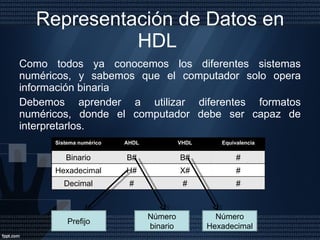

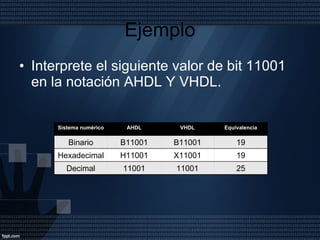

Este documento describe los dispositivos lógicos programables (PLD), incluyendo sus tipos, hardware, estructura interna y métodos de programación. Los PLD permiten modificar sus características mediante programación de hardware y automatizar procedimientos como tablas de verdad. Se detallan los tipos ROM, PROM, PLA, EEPROM, RAM y DRAM, así como la programación por ZIF y en sistema. Finalmente, se explican conceptos como la representación de datos en HDL y declaración de arreglos y vectores de bits.

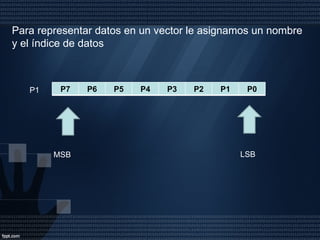

![Ejemplo Supongamos que hay un arreglo de 8 bits llamado P1 Escriba la designación para el bits mas significativo del arreglo Escriba la designación para el bits menos significativo del arreglo P1 MSB LSB Respuestas P1[7] P1[0] P1[7] 1P[6] P1[5] P1[4] P1[3] P1[2] P1[1] P1[0]](https://image.slidesharecdn.com/expodesd-120109224151-phpapp02/85/Programacion-PLD-20-320.jpg)

![Declaración de Arreglo de bits mediante AHDL La sintaxis para la declaración de arreglo , utiliza un nombre seguido del intervalo de las asignaciones de los índices las cuales van encerradas en corchetes y seguido de la palabra reservada input que significa dato de entrada. p1 [5…0] : INPUT;](https://image.slidesharecdn.com/expodesd-120109224151-phpapp02/85/Programacion-PLD-21-320.jpg)

![Declaración de variables intermedias Para declarar datos intermedios se declara justo después de las declaraciones de E/S Con un a variable y asignado el valor en el cuerpo del programa. VARIABLE nombre [3..0] : none; BEGIN temp [ ] = p1 []; END;](https://image.slidesharecdn.com/expodesd-120109224151-phpapp02/85/Programacion-PLD-22-320.jpg)