Diseño de Sistemas Digitales Prueba 1

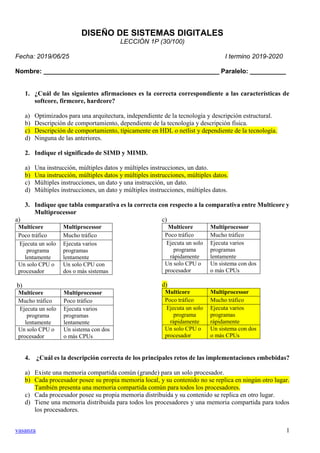

- 1. vasanza 1 DISEÑO DE SISTEMAS DIGITALES LECCIÓN 1P (30/100) Fecha: 2019/06/25 I termino 2019-2020 Nombre: _________________________________________________ Paralelo: __________ 1. ¿Cuál de las siguientes afirmaciones es la correcta correspondiente a las características de softcore, firmcore, hardcore? a) Optimizados para una arquitectura, independiente de la tecnología y descripción estructural. b) Descripción de comportamiento, dependiente de la tecnología y descripción física. c) Descripción de comportamiento, típicamente en HDL o netlist y dependiente de la tecnología. d) Ninguna de las anteriores. 2. Indique el significado de SIMD y MIMD. a) Una instrucción, múltiples datos y múltiples instrucciones, un dato. b) Una instrucción, múltiples datos y múltiples instrucciones, múltiples datos. c) Múltiples instrucciones, un dato y una instrucción, un dato. d) Múltiples instrucciones, un dato y múltiples instrucciones, múltiples datos. 3. Indique que tabla comparativa es la correcta con respecto a la comparativa entre Multicore y Multiprocessor a) Multicore Multiprocessor Poco tráfico Mucho tráfico Ejecuta un solo programa lentamente Ejecuta varios programas lentamente Un solo CPU o procesador Un solo CPU con dos o más sistemas b) Multicore Multiprocessor Mucho tráfico Poco tráfico Ejecuta un solo programa lentamente Ejecuta varios programas lentamente Un solo CPU o procesador Un sistema con dos o más CPUs c) Multicore Multiprocessor Poco tráfico Mucho tráfico Ejecuta un solo programa rápidamente Ejecuta varios programas lentamente Un solo CPU o procesador Un sistema con dos o más CPUs d) Multicore Multiprocessor Poco tráfico Mucho tráfico Ejecuta un solo programa rápidamente Ejecuta varios programas rápidamente Un solo CPU o procesador Un sistema con dos o más CPUs 4. ¿Cuál es la descripción correcta de los principales retos de las implementaciones embebidas? a) Existe una memoria compartida común (grande) para un solo procesador. b) Cada procesador posee su propia memoria local, y su contenido no se replica en ningún otro lugar. También presenta una memoria compartida común para todos los procesadores. c) Cada procesador posee su propia memoria distribuida y su contenido se replica en otro lugar. d) Tiene una memoria distribuida para todos los procesadores y una memoria compartida para todos los procesadores.

- 2. vasanza 2 5. ¿Cuál es la descripción correcta de los principales retos de las implementaciones embebidas? a) Procesamiento de imágenes b) Procesamiento de señales c) Control en tiempo real d) a y b e) b y c f) a, b y c g) a y c 6. Indique cual es el resultado que se debe imprimir a) 241.4 b) 124.2 c) 214.4 d) 241.2 7. Seleccione la descripción correcta de los bits del registro de control status en el procesador NIOSii. a) RSIE es el bit de activación de interrupción del conjunto de registros y NMI es el bit de modo de interrupción enmascarable. b) IL es el campo de nivel de interrupción y NMI es el bit de modo de interrupción no enmascarable. c) IL es el campo de nivel de interrupción y NMI es el bit de modo de interrupción enmascarable. d) RSIE es el bit de control de interrupción del conjunto de registros e IL controla el nivel en que se da interrupciones no enmascarables se da servicio.

- 3. vasanza 3 8. ¿Cuál es el orden correcto de las tareas básicas que ejecuta el procesador durante interruption services routine (ISR)? a) Optimizar el estado del sistema, transferir el control a una rutina especial y reanudar la ejecución normal del programa. b) Suspender la ejecución del programa actual, manejar la excepción y guardar el estado actual del sistema. c) Suspender la ejecución del programa actual, transferir el control a una rutina especial y restaurar el estado del sistema. d) Ninguna de las anteriores. 9. Indique cual es el resultado que se debe imprimir de: value of var variable, adress stored in ip variable y value of *ip variable a) 20,0xbfc601ac,10 b) 20,0xbfc601ac,20 c) 30,0xbfc601ac,30 d) 20,0xbfc601ac,0

- 4. vasanza 4 10. Indique que tabla comparativa es la correcta con respecto a la comparativa de parámetros de arquitectura RISC vs CISC. a) Parámetro RISC CISC Ejecución de instrucción En paralelo Secuencial Modos de direccionamiento Complejo Simple Duración de una instrucción 4-120 ciclos Muchos ciclos b) Parámetro RISC CISC Tipos de instrucciones Simple Complejo Modos de direccionamiento Complejo Simple Ejecución de instrucciones En paralelo Secuencial c) Parámetro RISC CISC Formato de instrucción Fija Variable Modos de direccionamiento Complejo Simple Conjunto de registros Único Muchos registros d) Parámetro RISC CISC Ejecución de instrucción En paralelo Secuencial Modos de direccionamiento Simple Complejo Duración de una instrucción Un ciclo Muchos ciclos