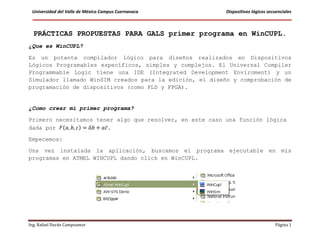

Este documento describe cómo crear un primer programa en WinCUPL para diseñar circuitos lógicos programables. Explica que WinCUPL es un compilador lógico que incluye un entorno de desarrollo integrado y un simulador. Luego detalla los pasos para crear un nuevo proyecto, especificar las entradas, salidas y función lógica, compilar el diseño y generar un archivo de programa para cargar en un dispositivo programable. También muestra ejemplos de cómo implementar funciones lógicas básicas como inversores