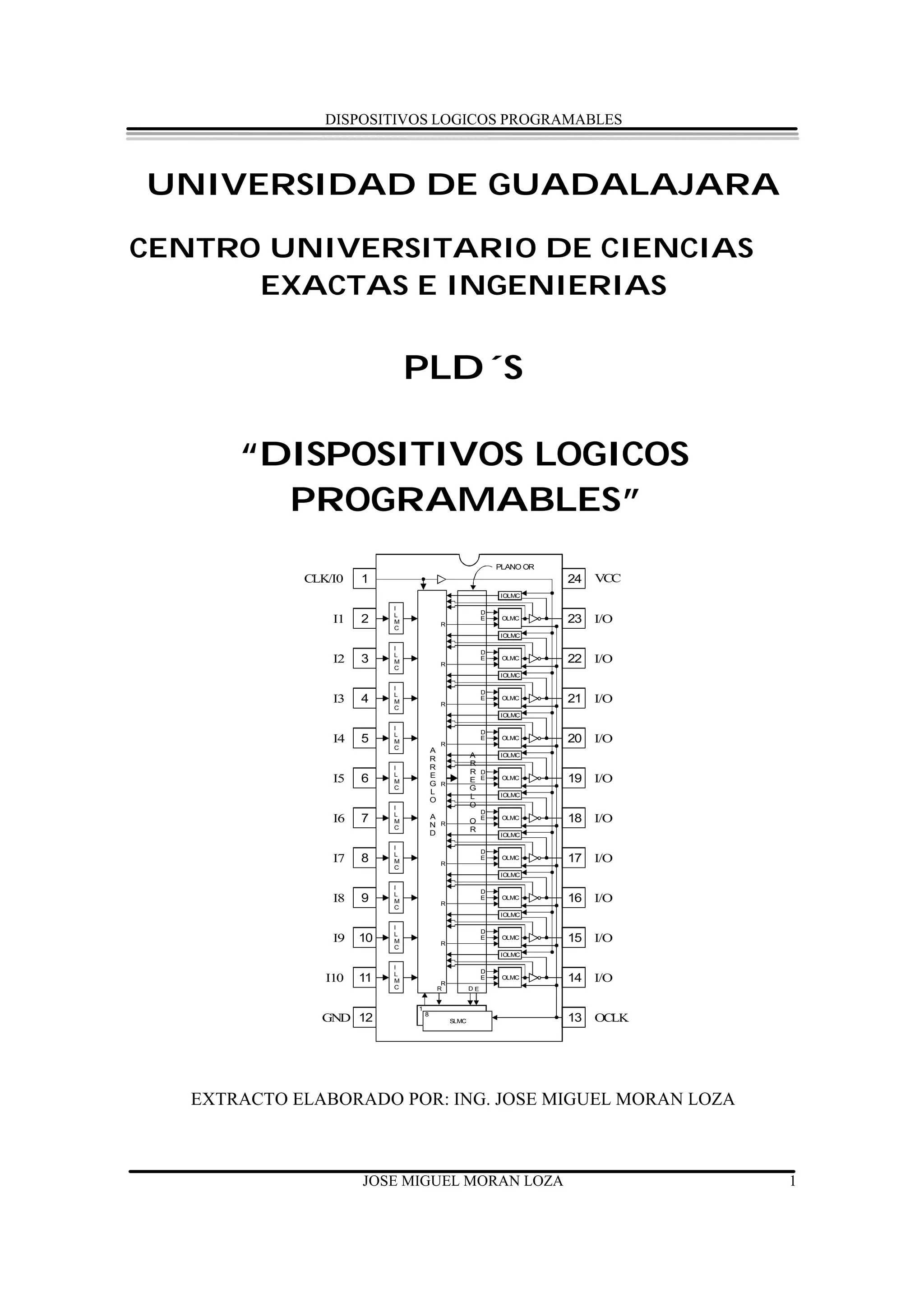

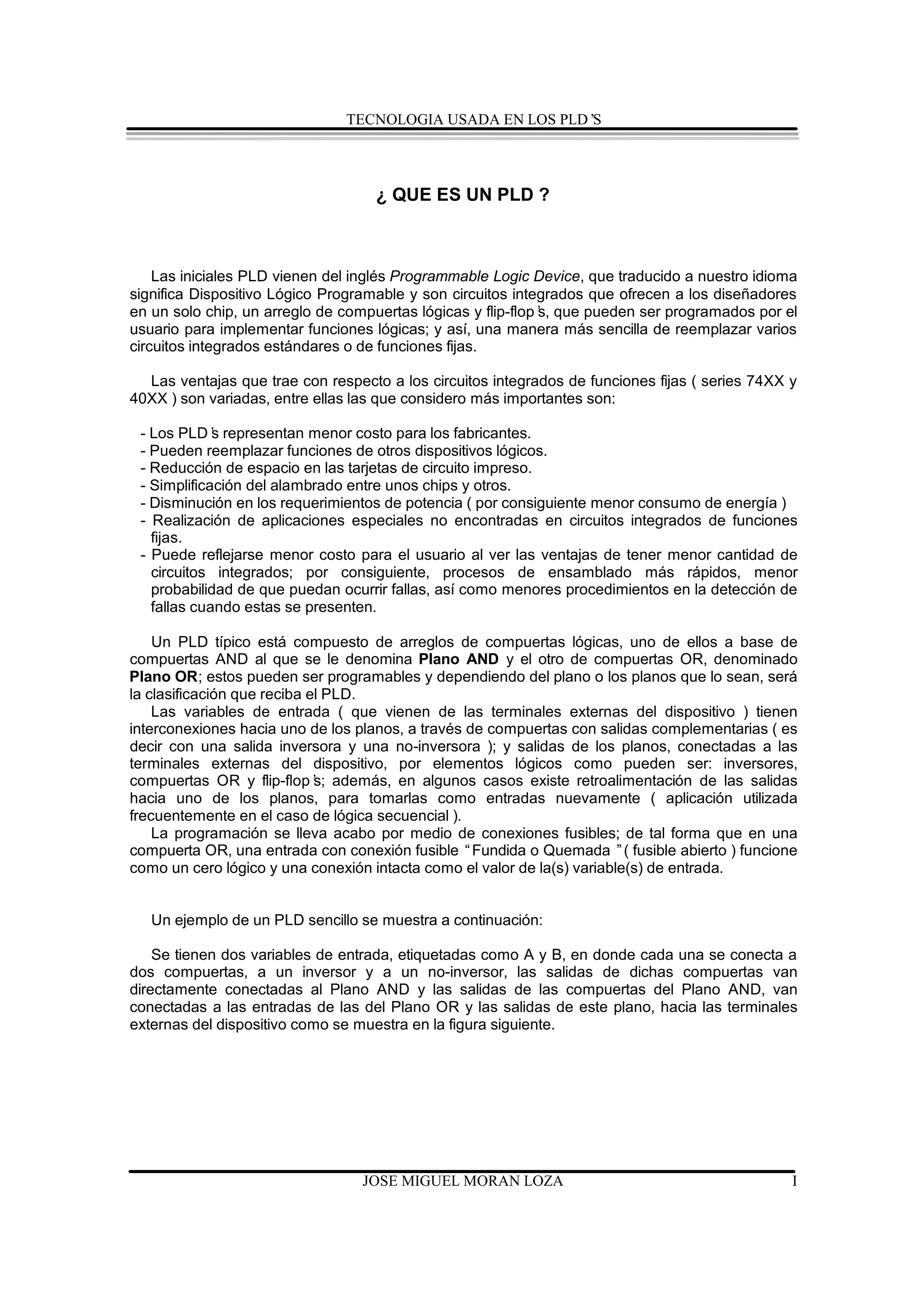

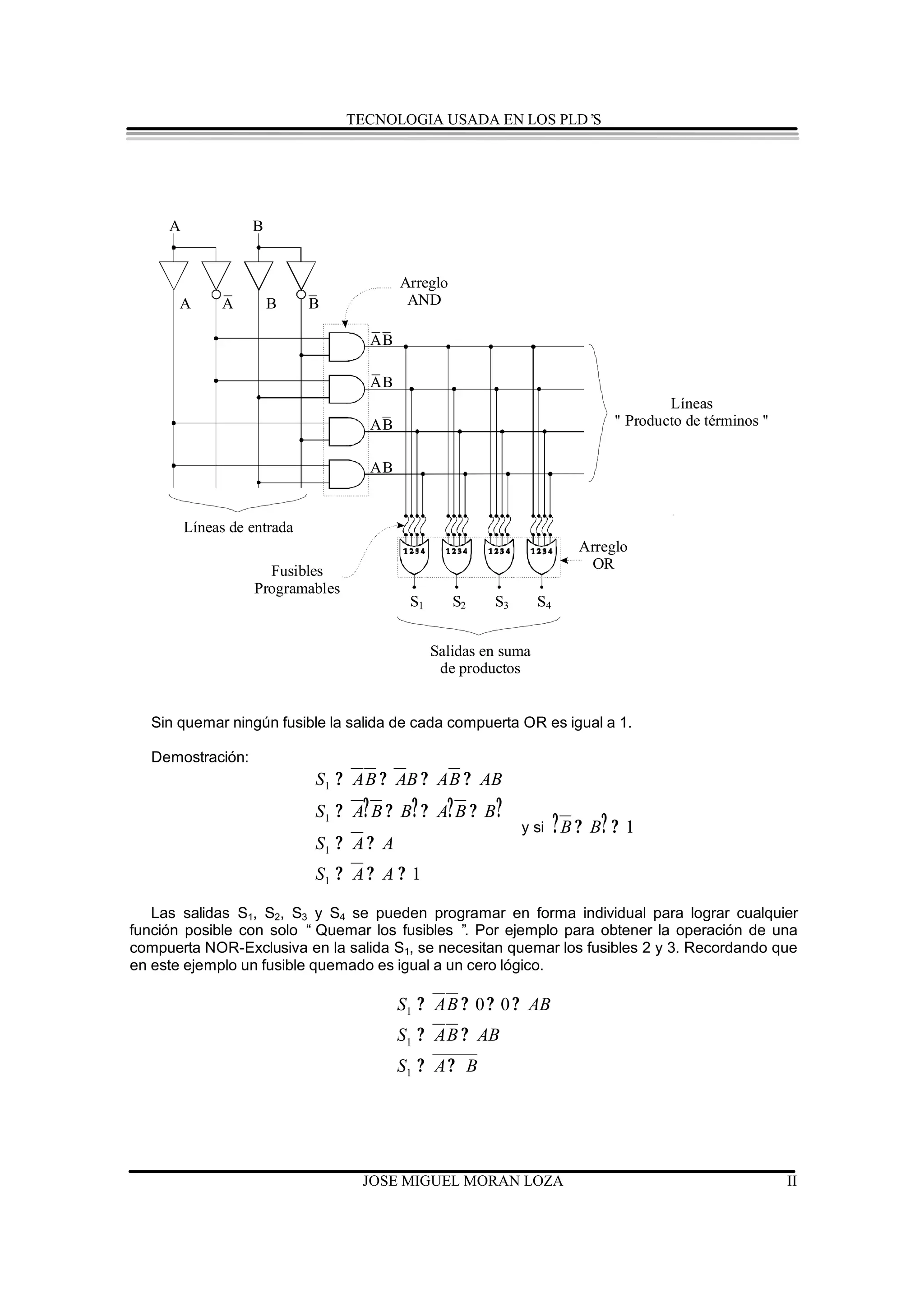

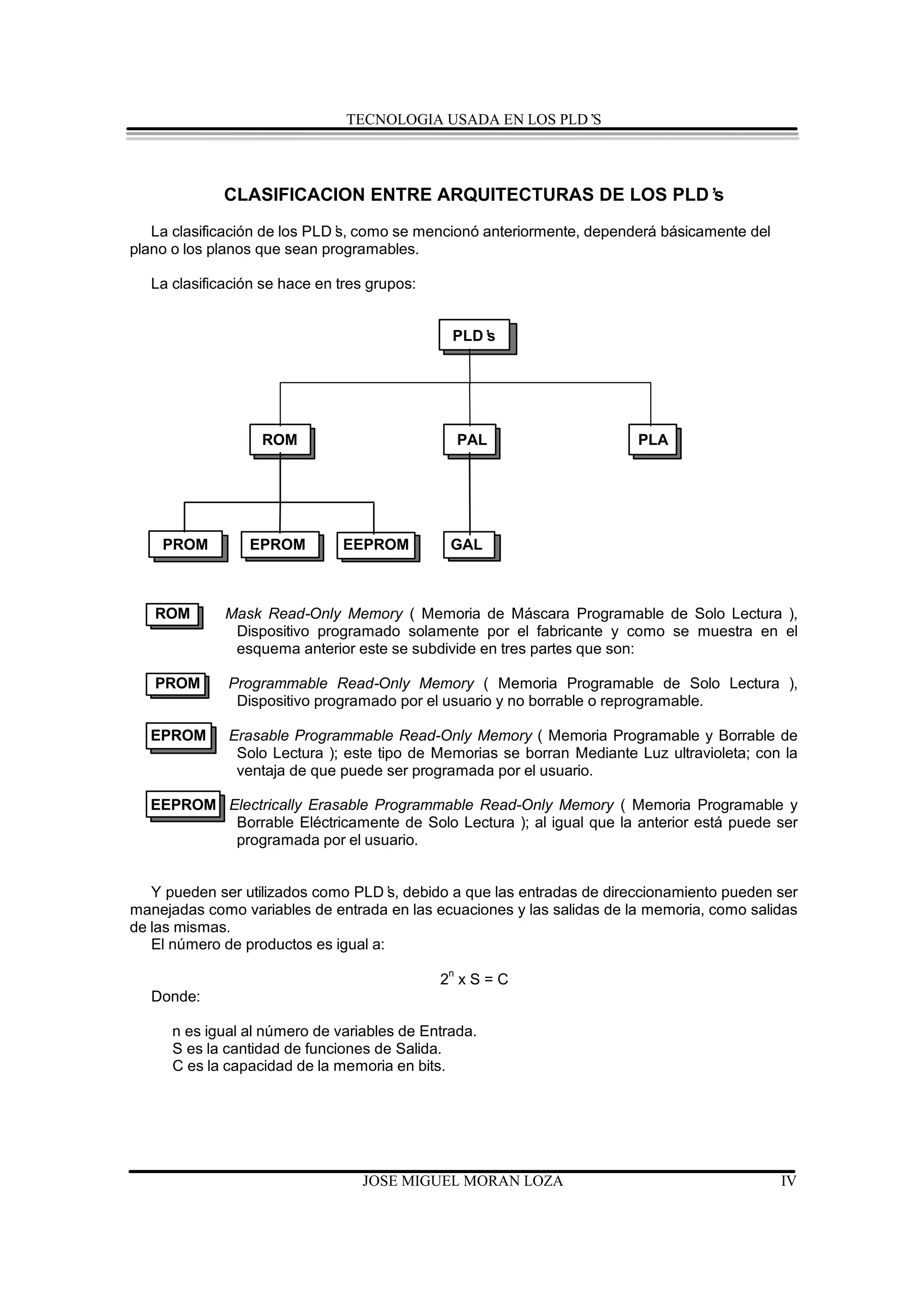

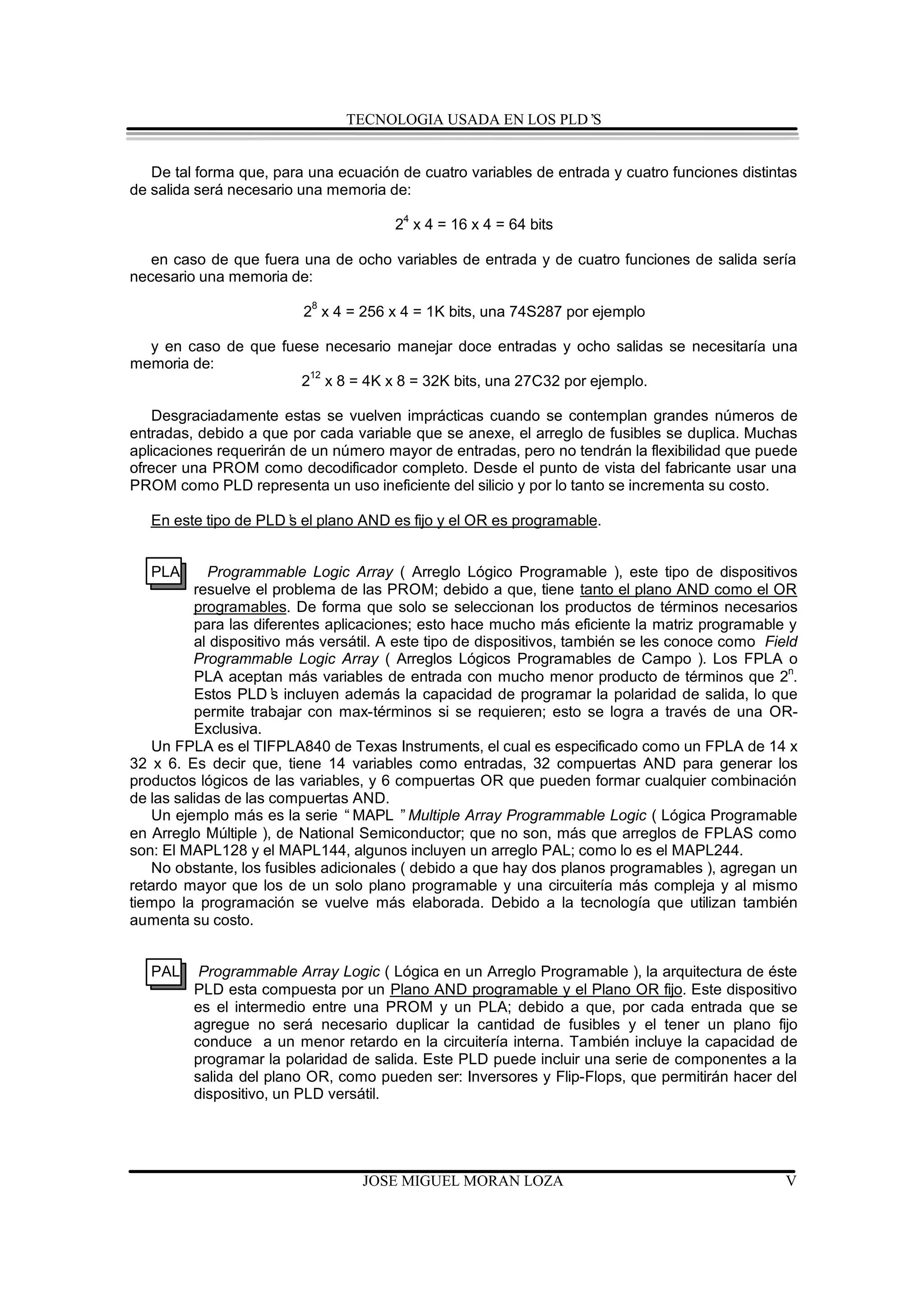

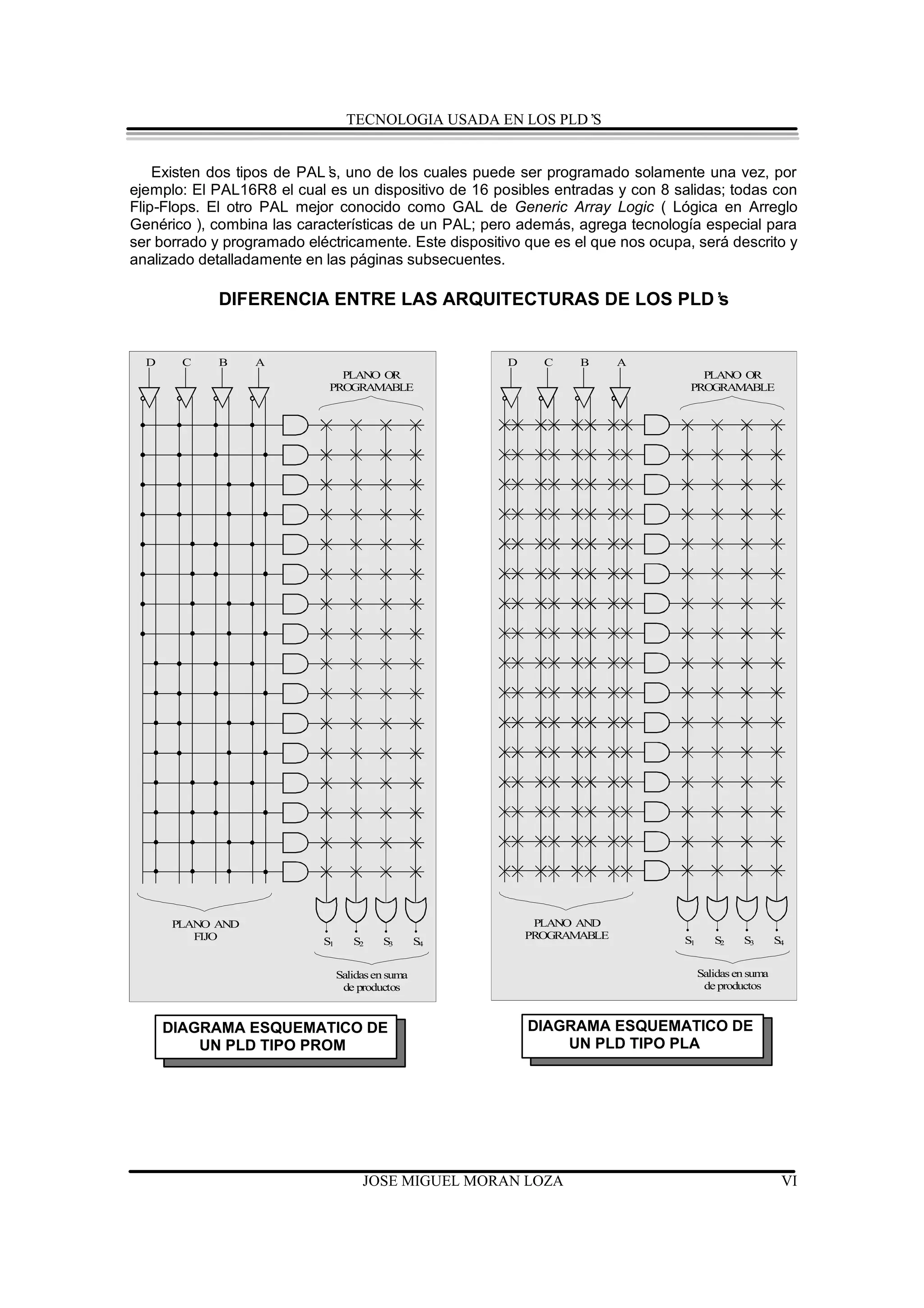

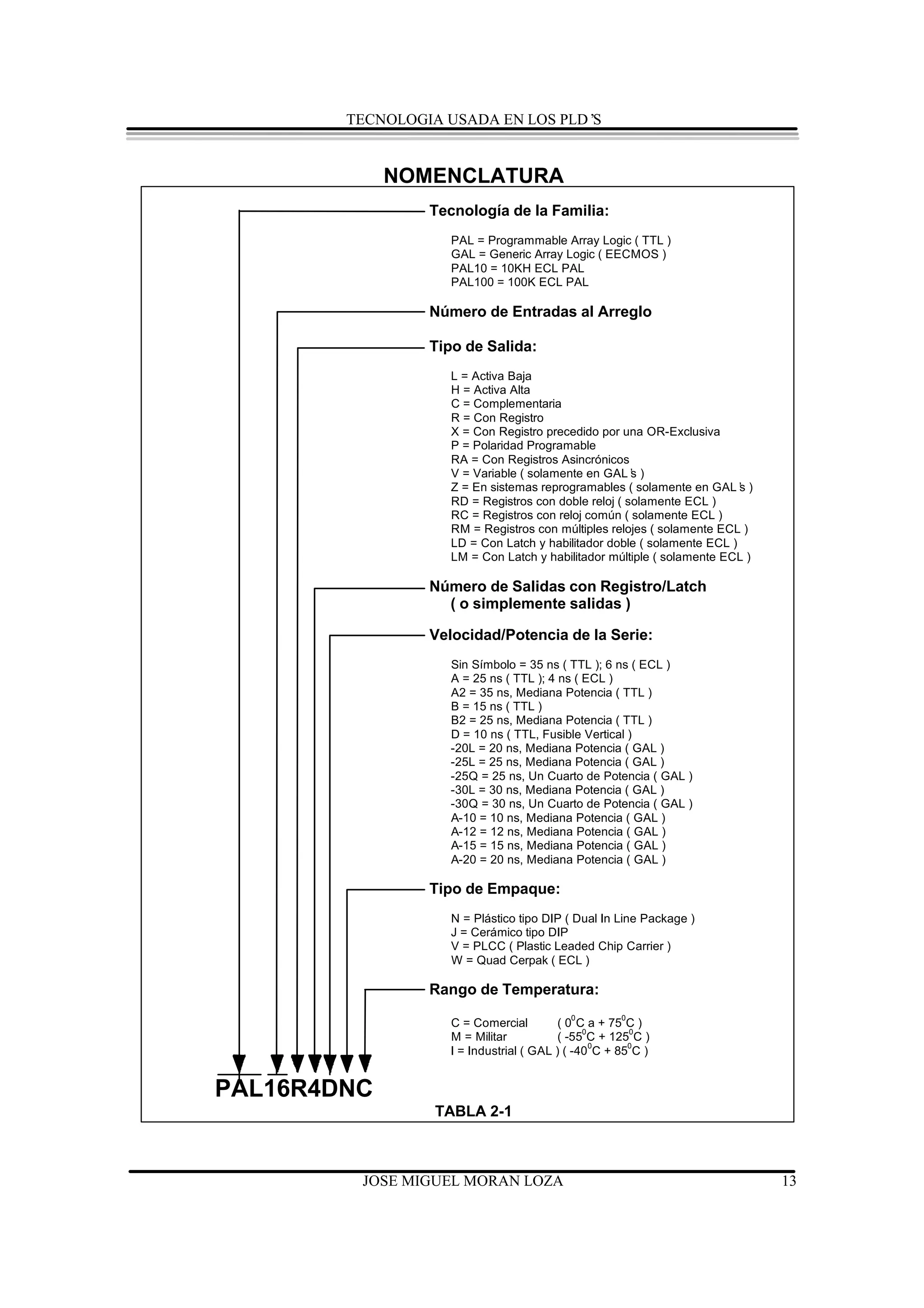

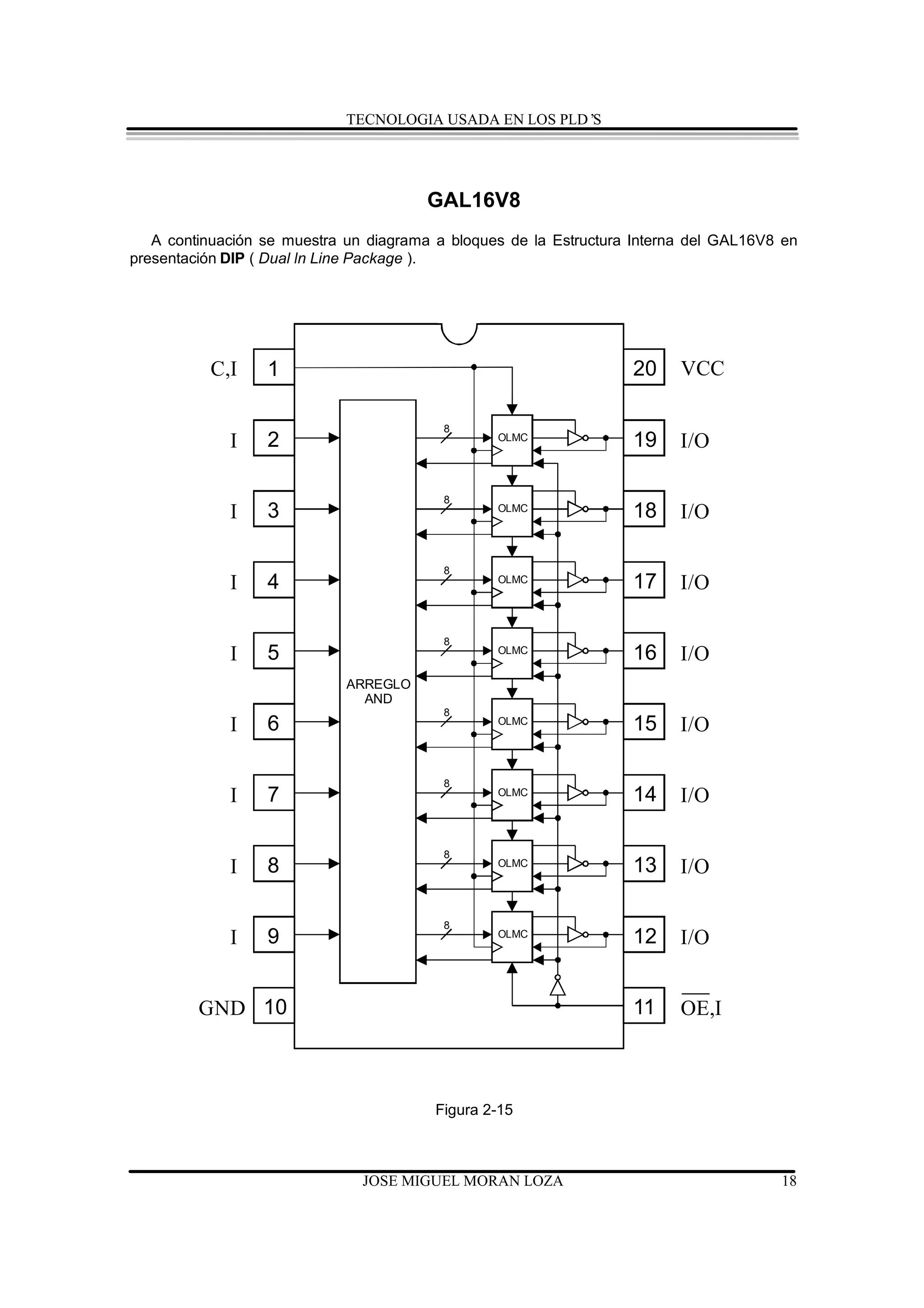

Este documento describe los dispositivos lógicos programables (PLD). Explica que los PLD son circuitos integrados que ofrecen arreglos de compuertas lógicas y flip-flops programables por el usuario para implementar funciones lógicas. Luego resume las principales clasificaciones de PLD, incluyendo PROM, PAL y PLA, distinguiéndolos por si sus planos AND y OR son fijos o programables. Finalmente, contrasta las arquitecturas de PAL y PLA, señalando que PAL tiene plano AND