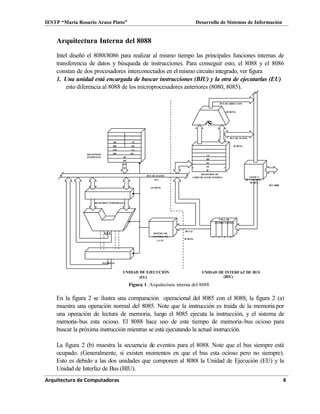

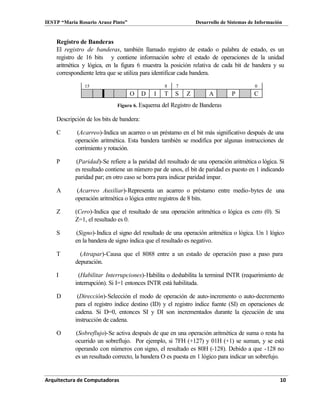

El documento describe la arquitectura del microprocesador Intel 8088/8086. Consta de dos unidades principales: la Unidad de Interfaz de Bus que busca instrucciones de forma concurrente para mantener llena una cola de instrucciones, y la Unidad de Ejecución que ejecuta las instrucciones. El 8088 incluye 14 registros como el Acumulador, Contador y registros de segmentos para direccionar la memoria.