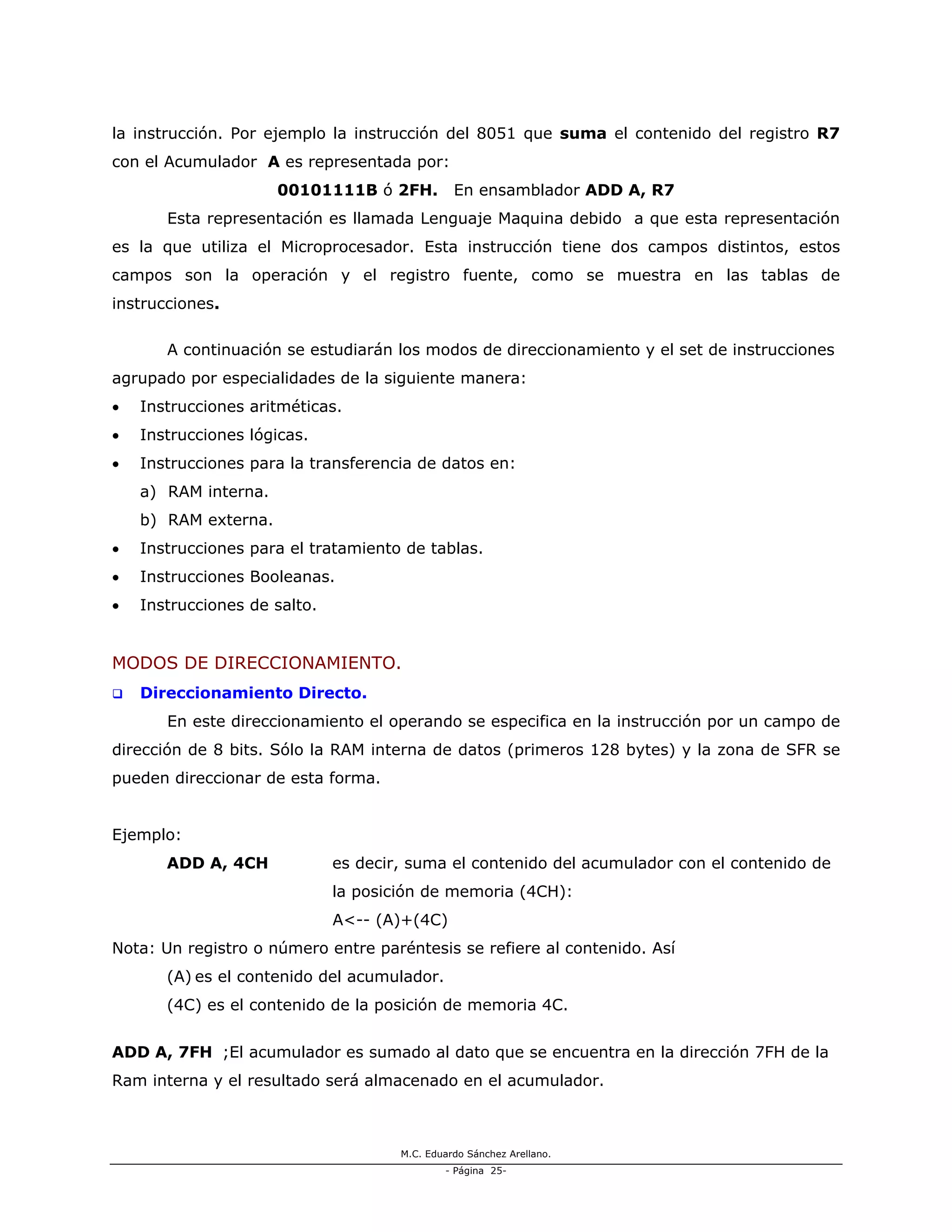

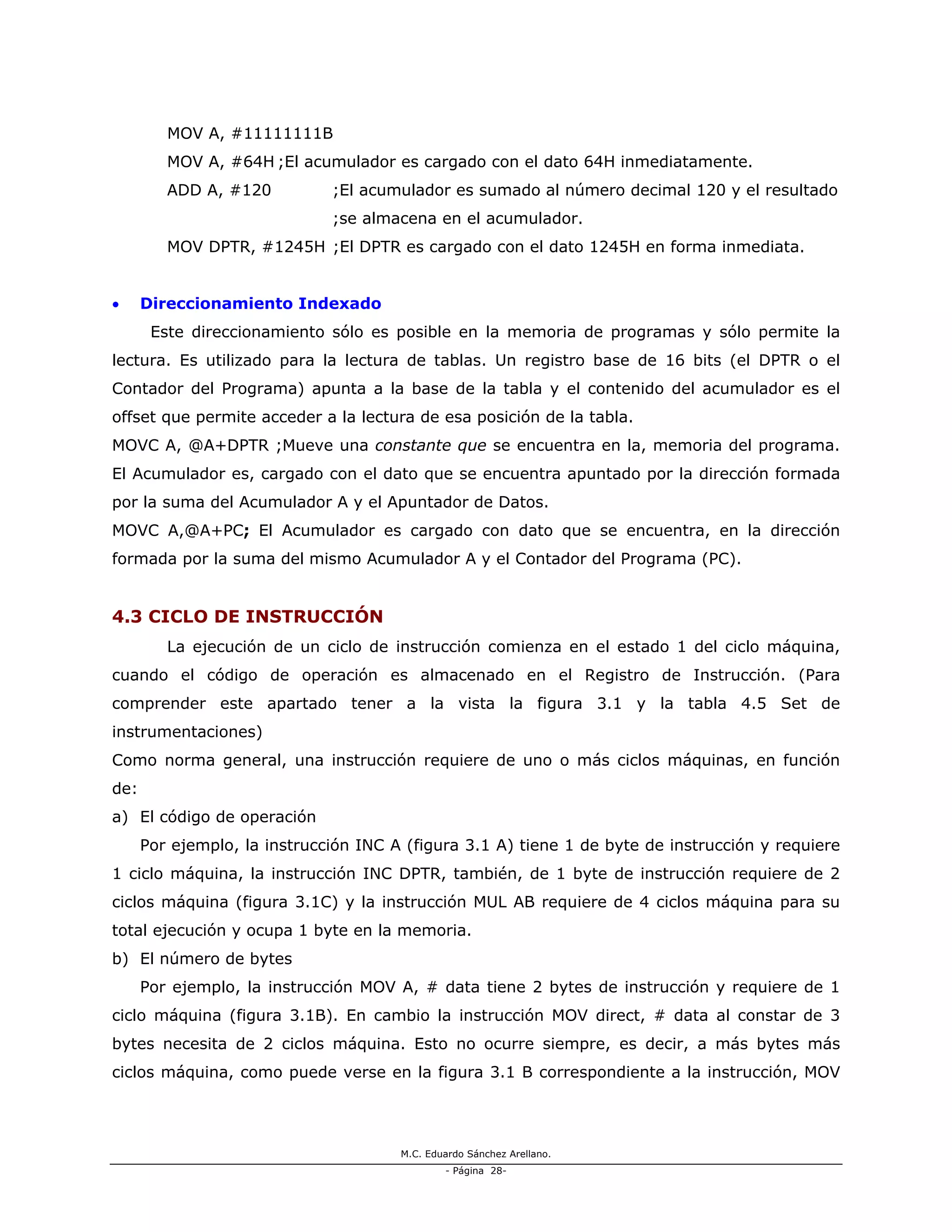

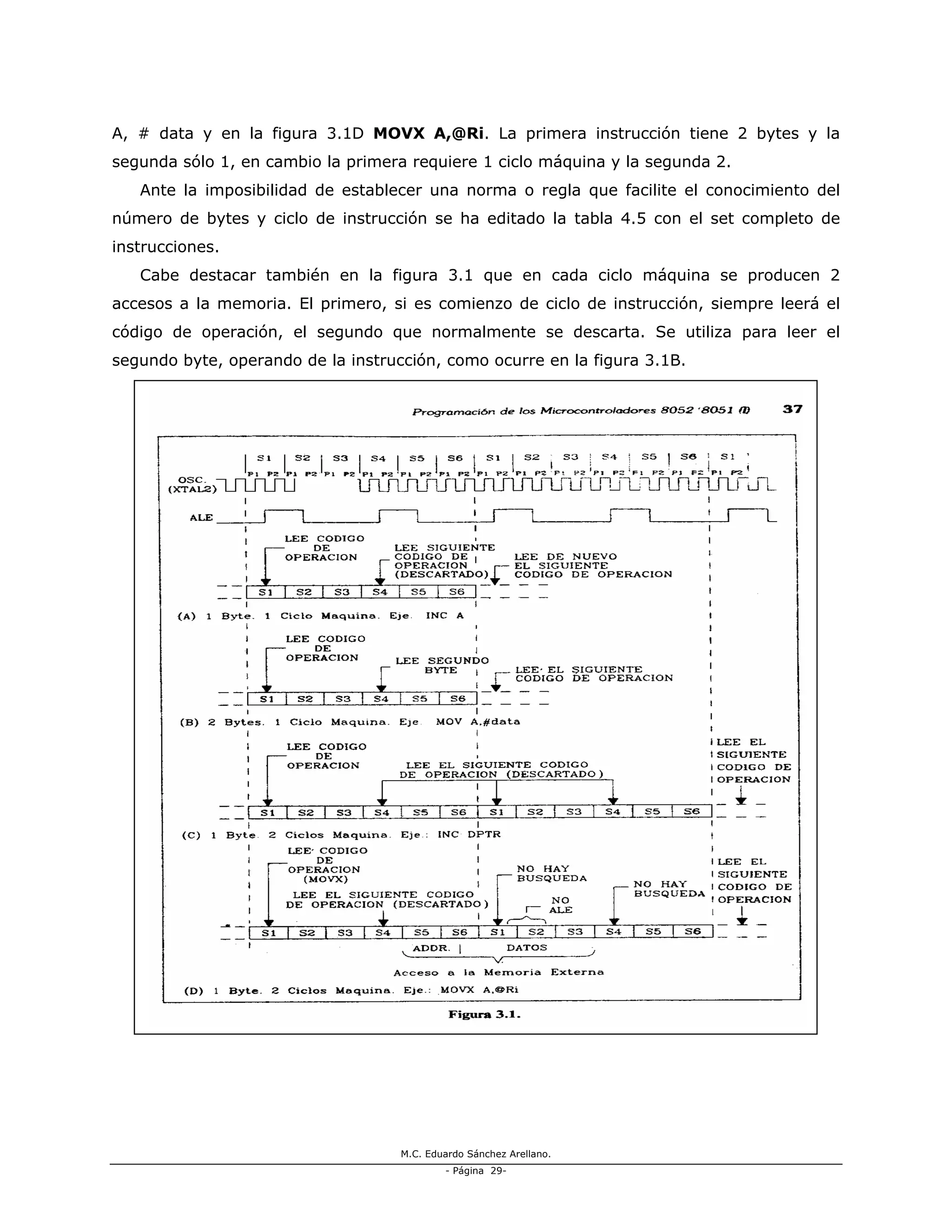

El documento detalla un curso sobre microcontroladores, enfocado en la familia MCS-51, incluyendo características, programación, configuración de memoria y control de puertos de entrada/salida. Se exploran capítulos sobre la historia de los microprocesadores, su evolución, y se proporcionan manuales y anexos relevantes. El contenido está diseñado para ofrecer una comprensión profunda de los principios fundamentales de los microcontroladores y su aplicación práctica.

![M.C. Eduardo Sánchez Arellano.

- Página 31-

En algunas tablas no son afectados los flags, y esto se indica con un mensaje en la

parte inferior de las mismas.

Los tiempos de ejecución Se han tomado utilizando como referencia una frecuencia

de reloj de 12 MHz.

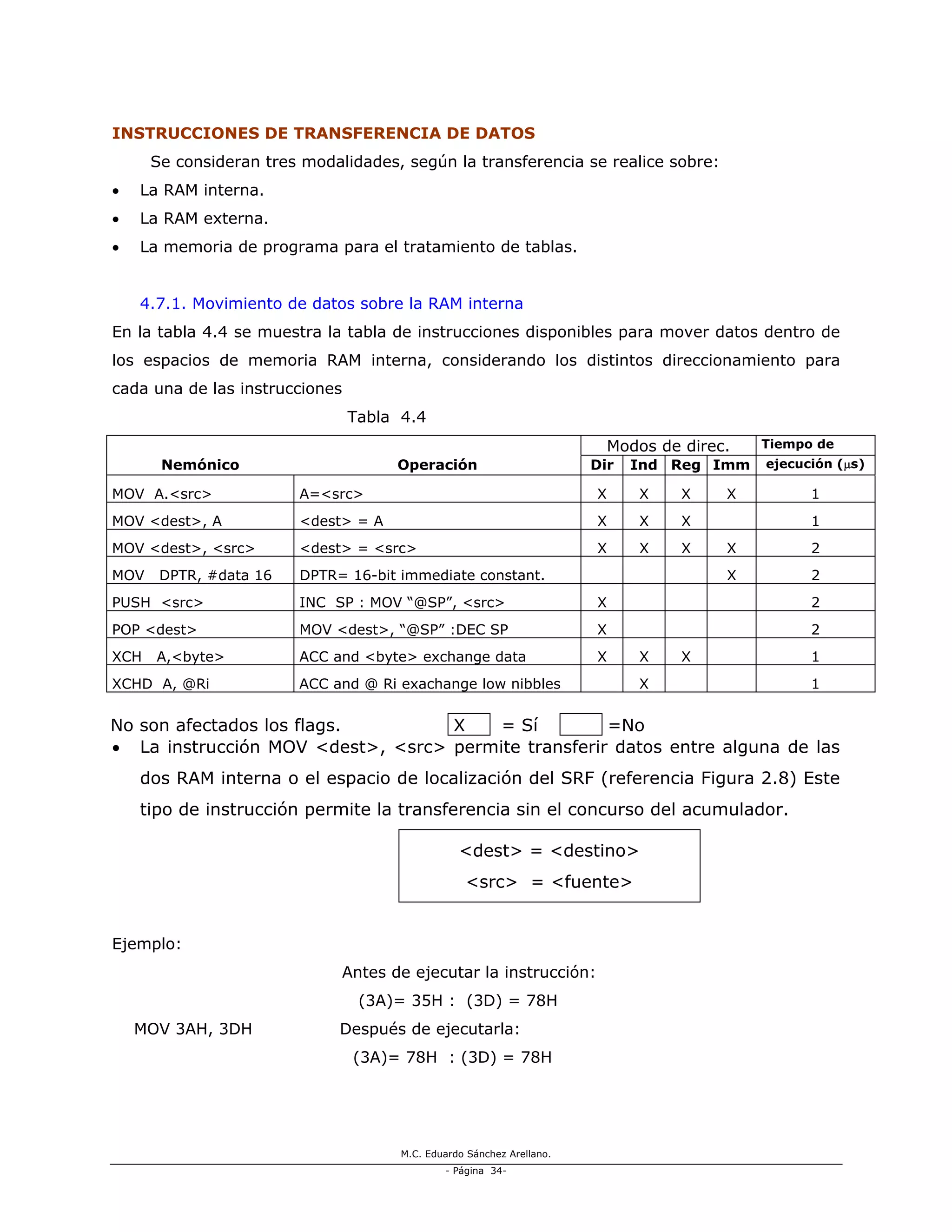

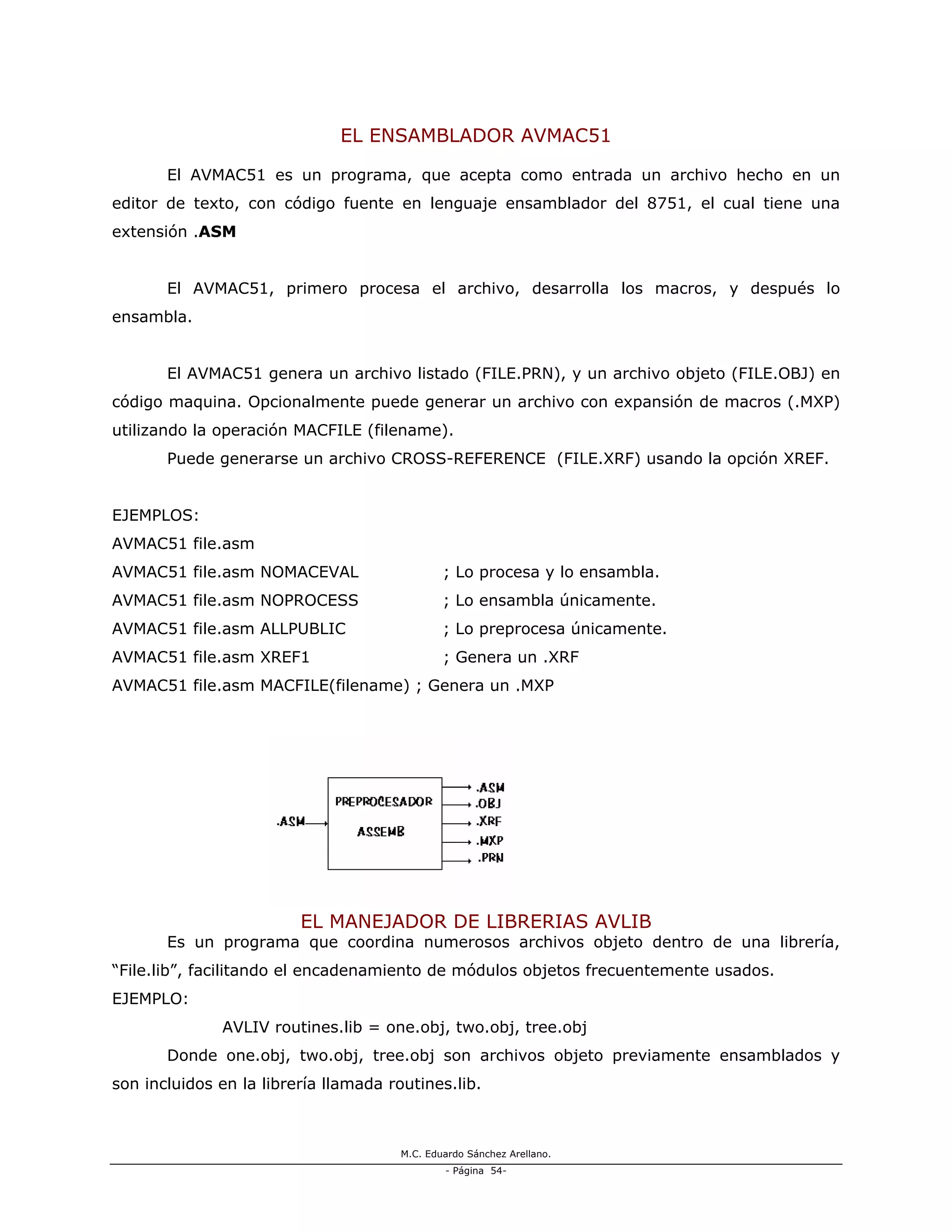

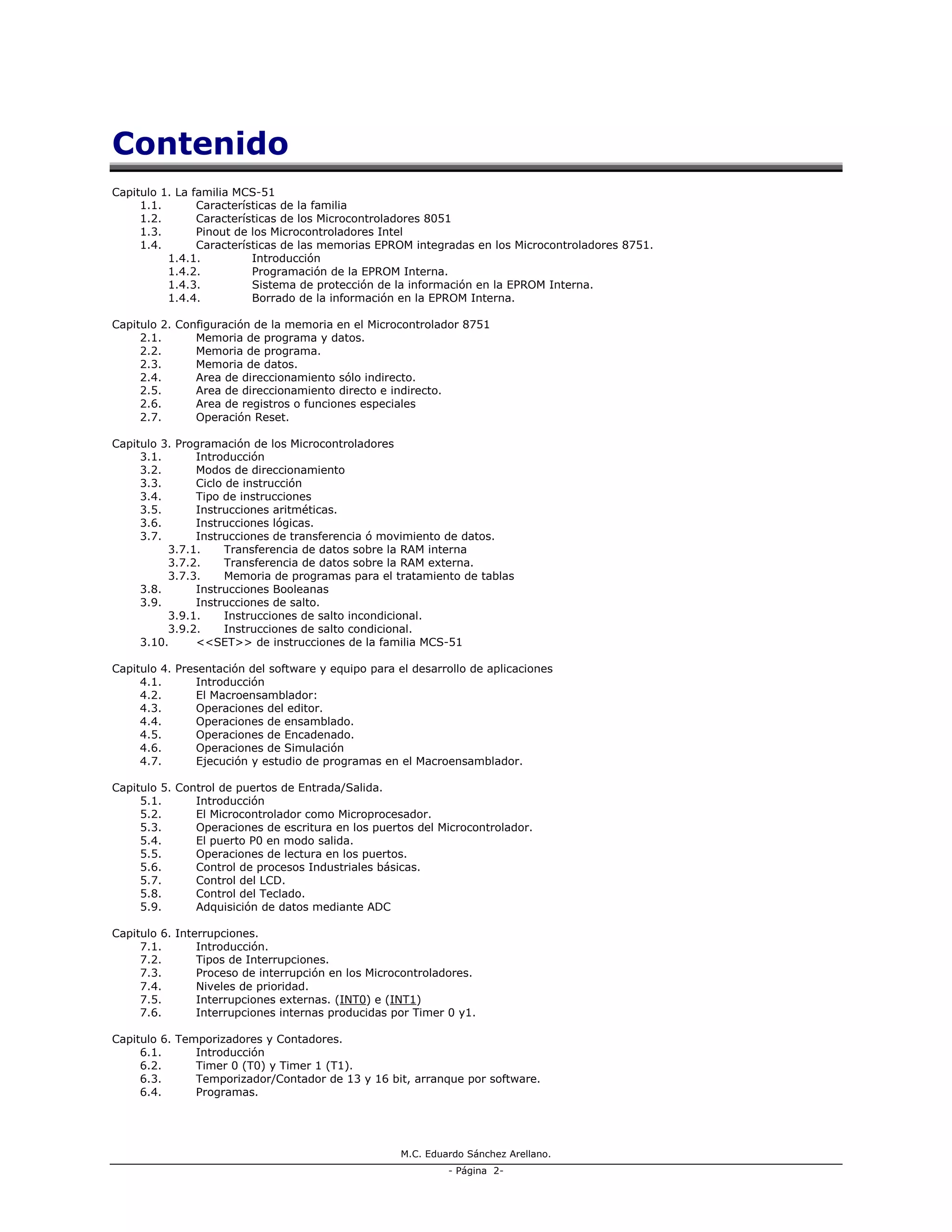

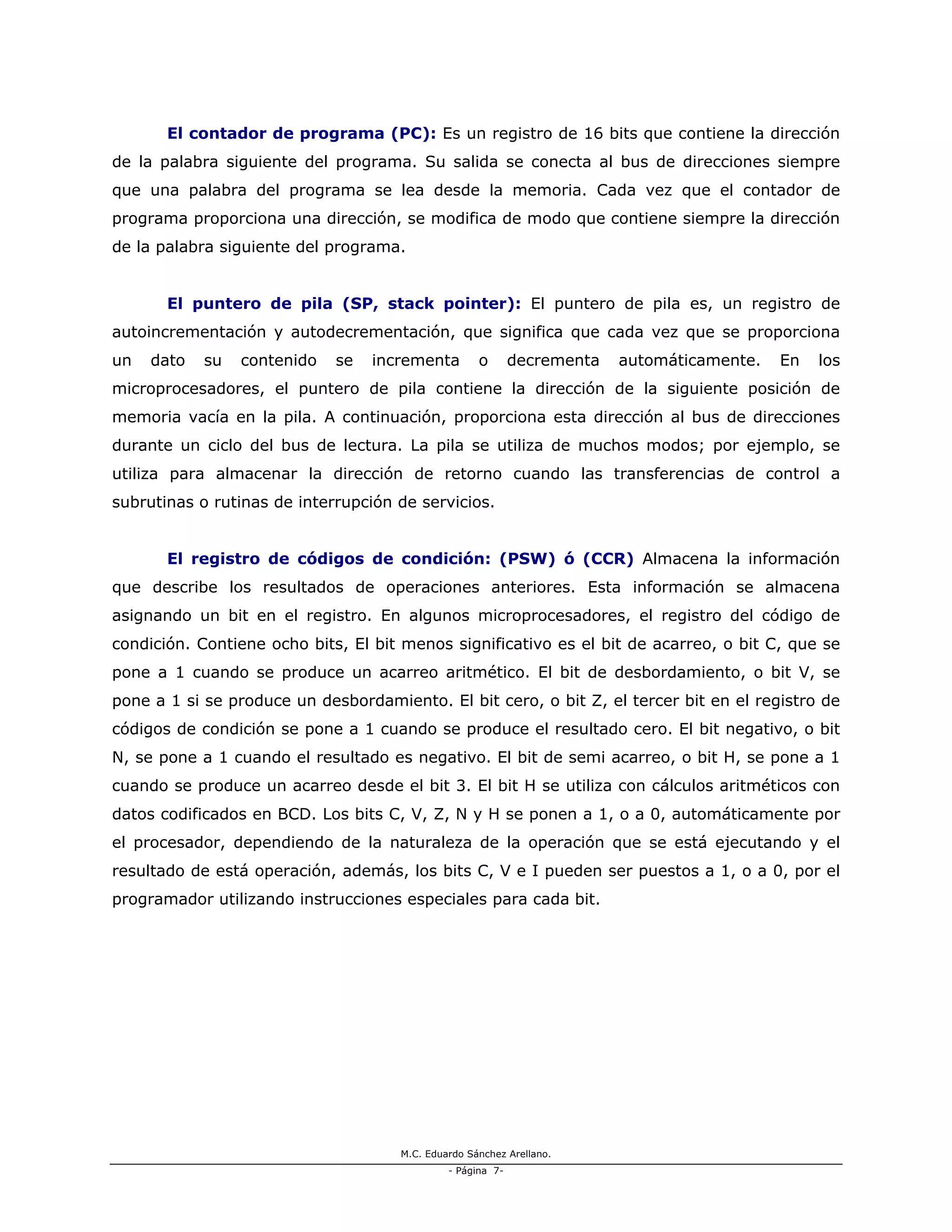

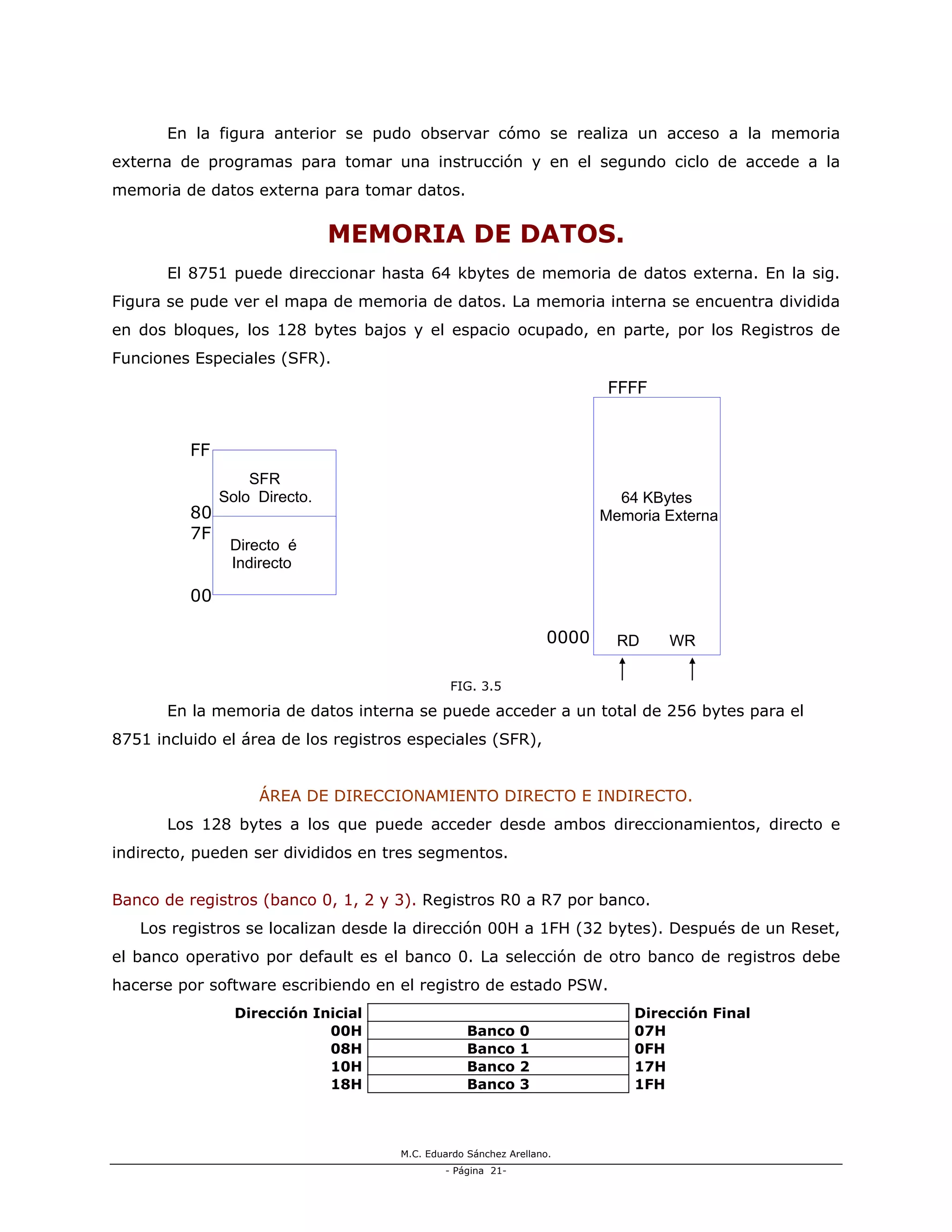

3.5 INSTRUCCIONES ARITMETICAS

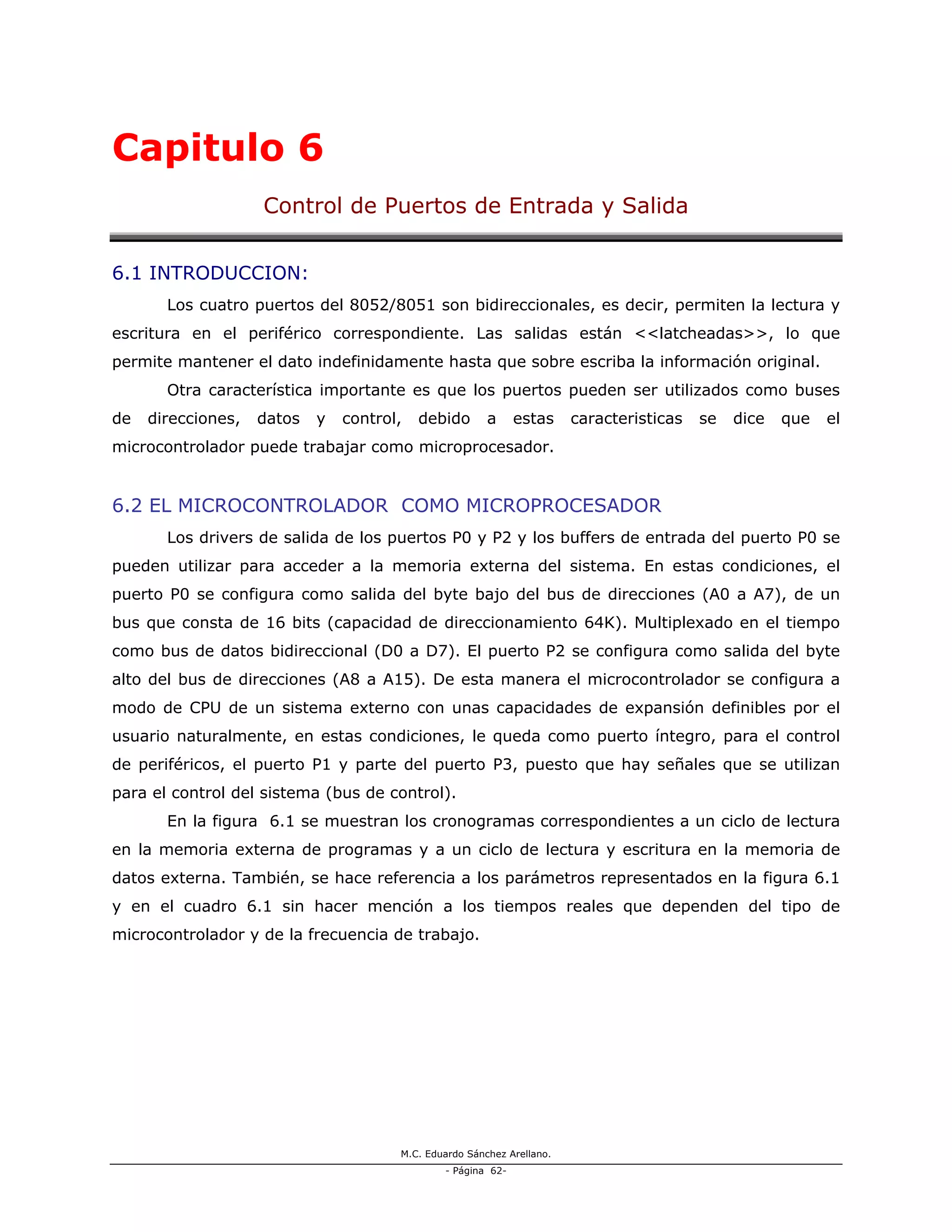

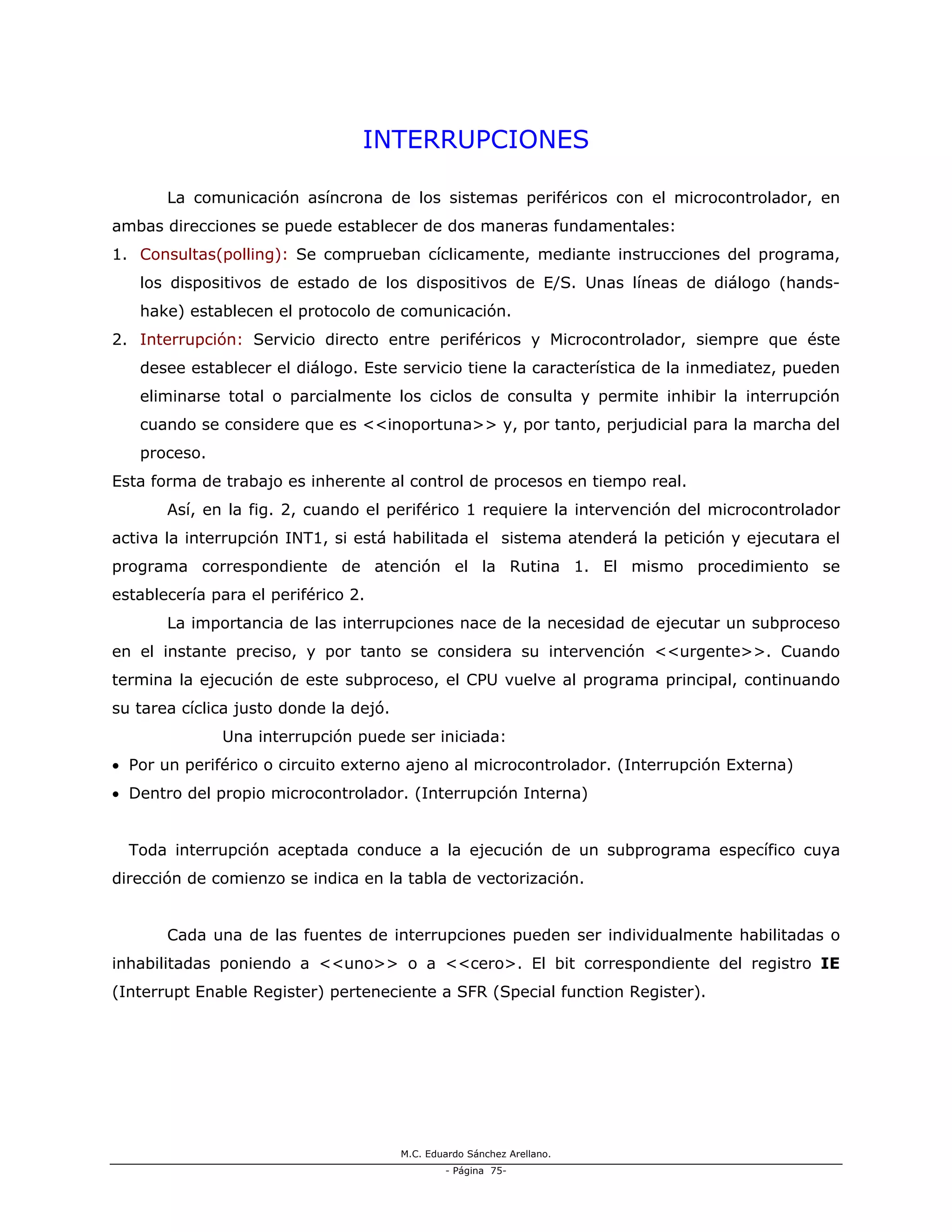

En la tabla 4.2. Se muestra el menú de las instrucciones aritméticas. Se indican en la

tabla los modos de direccionamiento que permite la instrucción y los flags afectados.

Los tiempos de ejecución que se indican en la tabla están evaluados sobre una

frecuencia de reloj de 12 MHz.

Nemónico Operación Modos de direccionamiento Tiempo de

Ejecución

Flag afectados

Dir Ind Reg Imm µs C OV AC

ADD A,<byte> A=A+<byte> X X X X 1 X X X

ADDC A,<byte> A=A+<byte>+C X X X X 1 X X X

SUBB A,<byte> A=A-<byte>-C X X X X 1 X X X

INC A A=A+1 Accumulator only 1

INC <byte> <byte>=<byte>+1 X X X 1

INC DPTR DPTR=DPTR+1 Data pointer only 2

DEC A A=A-1 Accumulator only 1

DEC <byte> <byte> = <byte> -1 X X X 1

MUL AB B:A = B x A ACC and B only 4 0 X

DIV AB A = int [A/B]

B = Mod [A/B]

ACC and B only 4 0 X

DA A Decimal Adjust Accumulator only 1 X

Tabla 4.2

X =Si =No

Al leer dicha tabla se observa que:

• Se puede incrementar o decrementar un byte en la memoria de datos interna sin la

intervención del acumulador.

• Una de las instrucciones INC opera sobre los 16 bits del puntero de datos (DPTR).

• La instrucción MUL AB multiplica el contenido del acumulador con el dato situado en el

registro B y el producto, en formato 16 bits, aparece en los registros Acumulador y B

(Sobreescribe a los operandos).

• La instrucción DIV AB divide el contenido del acumulador con el dato contenido en B,

apareciendo el resultado, cociente, en el acumulador y el resto en el registro B.](https://image.slidesharecdn.com/curso20microcontroladores-1221680878782491-9/75/Curso-de-microcontrolador-MCS51-31-2048.jpg)

![M.C. Eduardo Sánchez Arellano.

- Página 32-

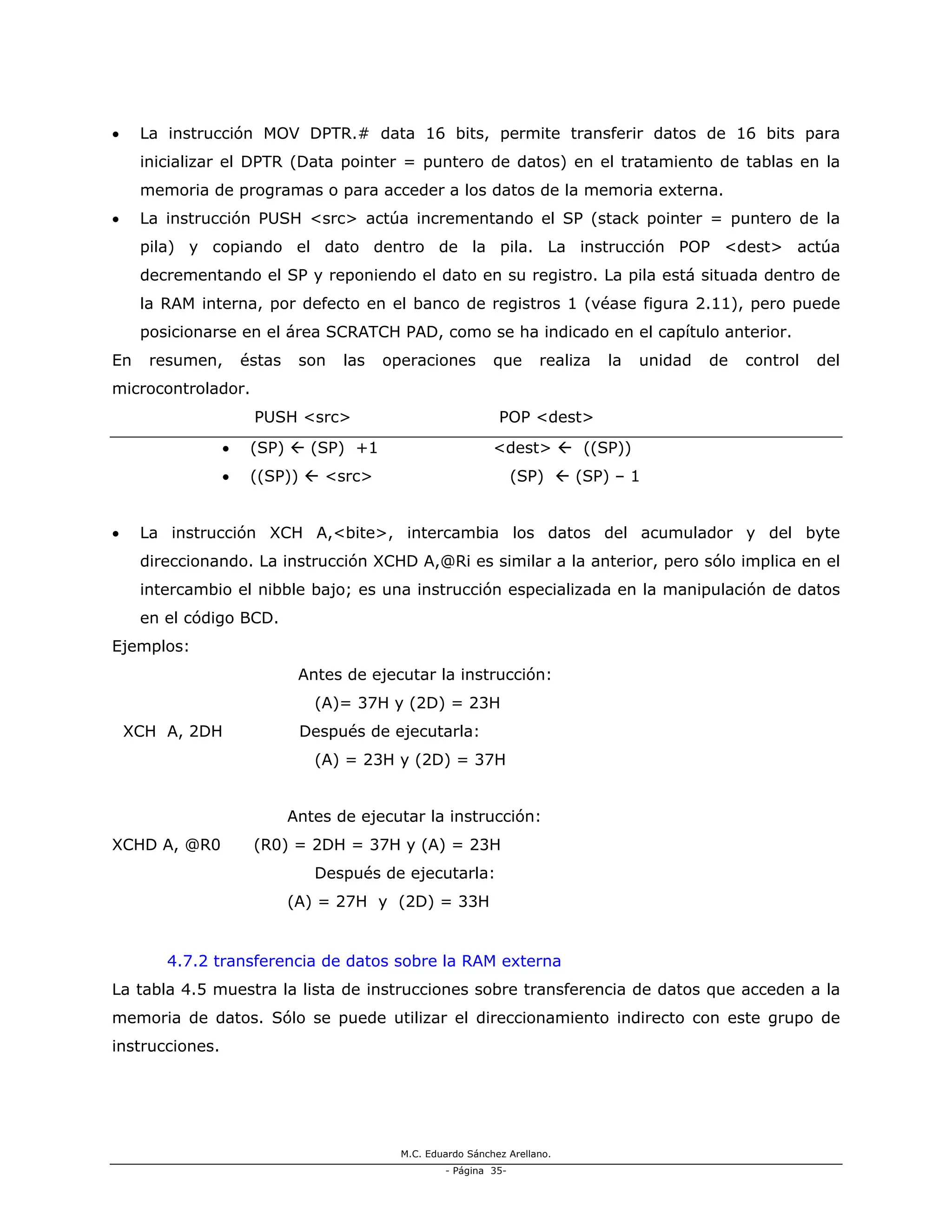

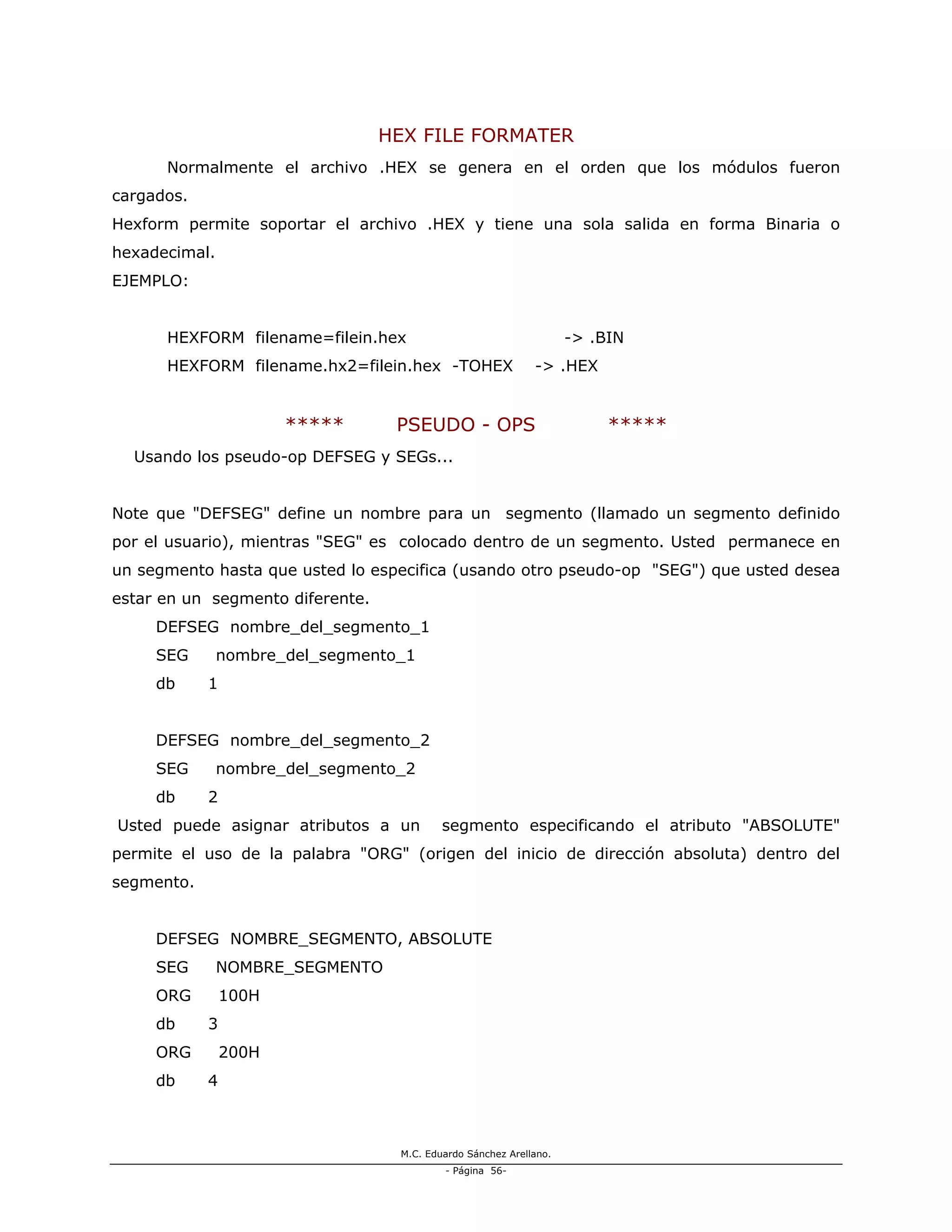

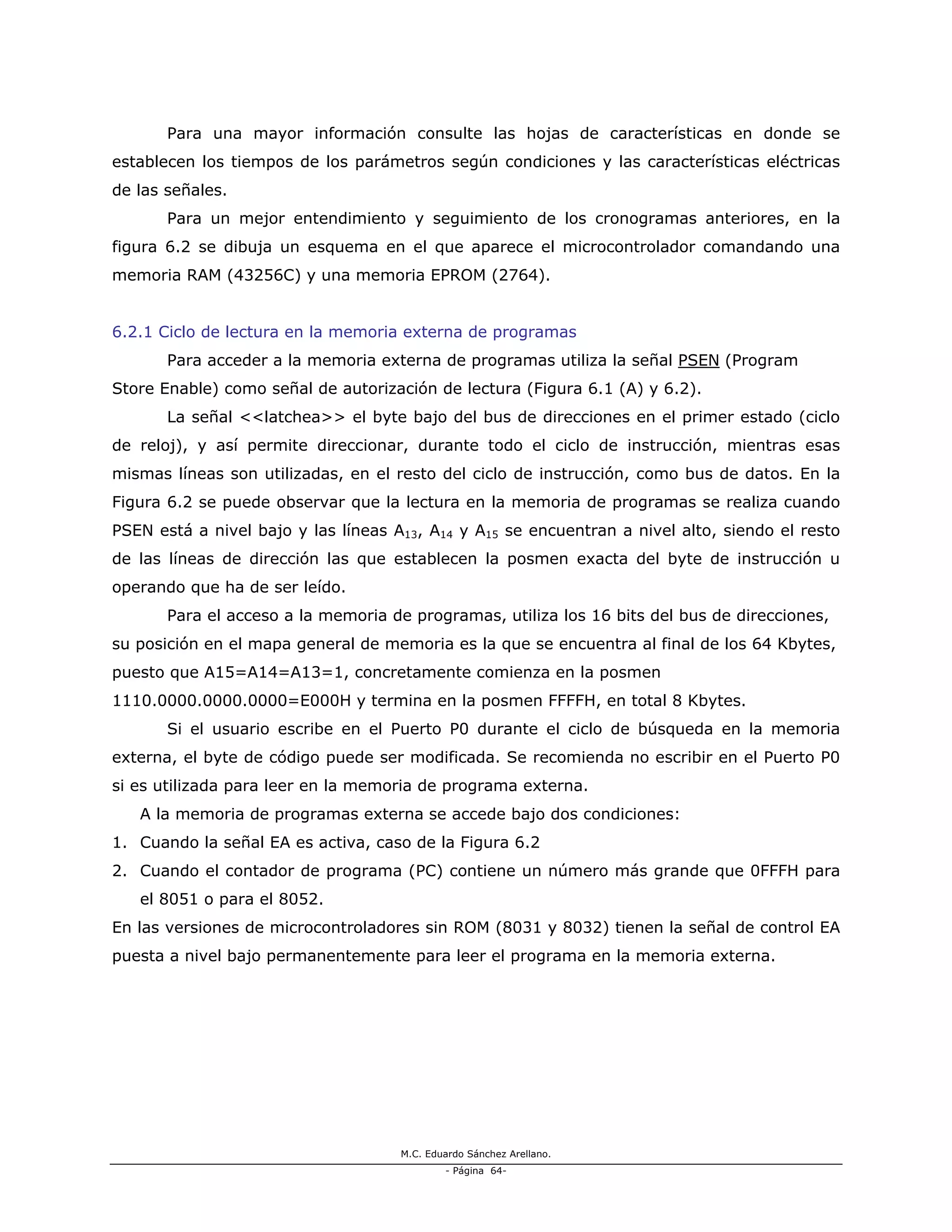

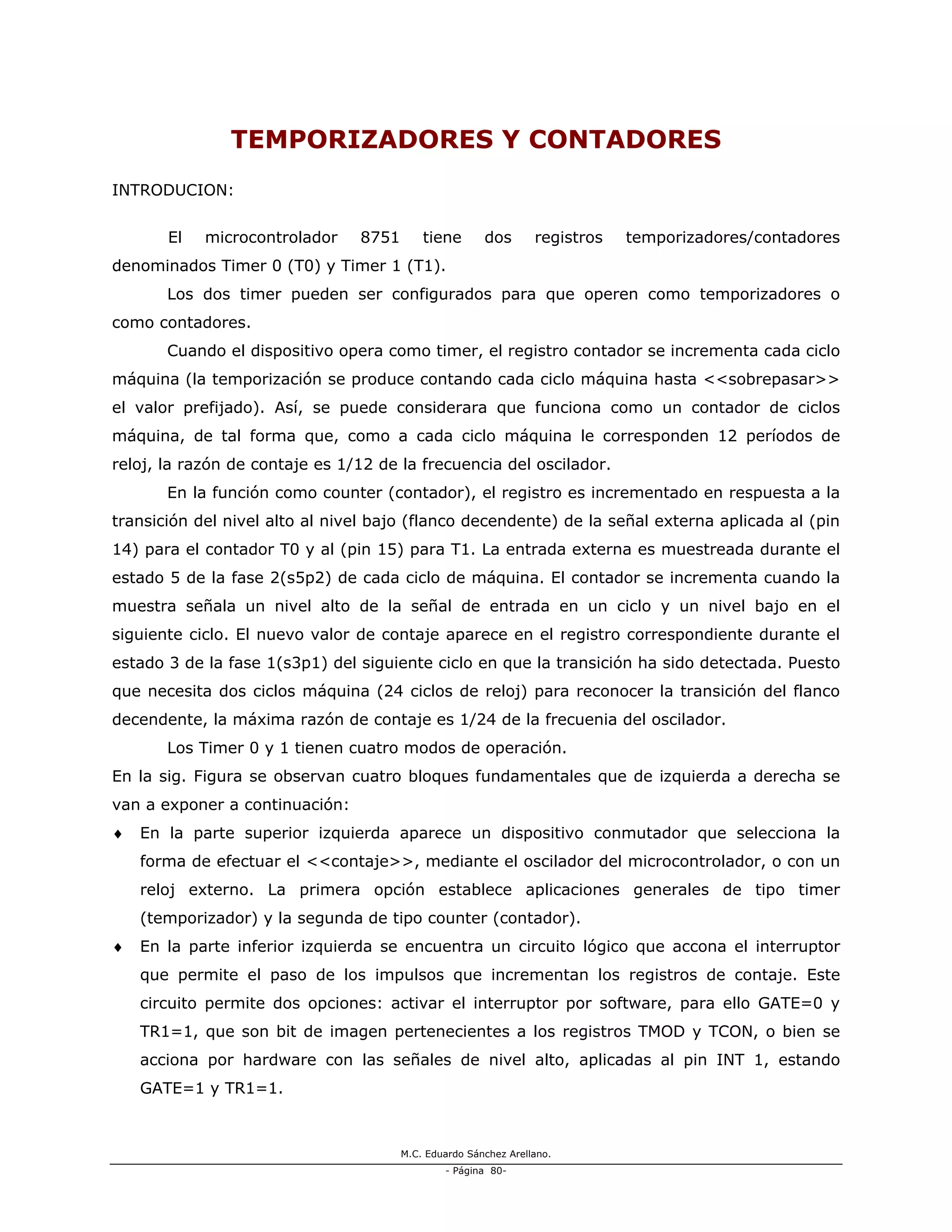

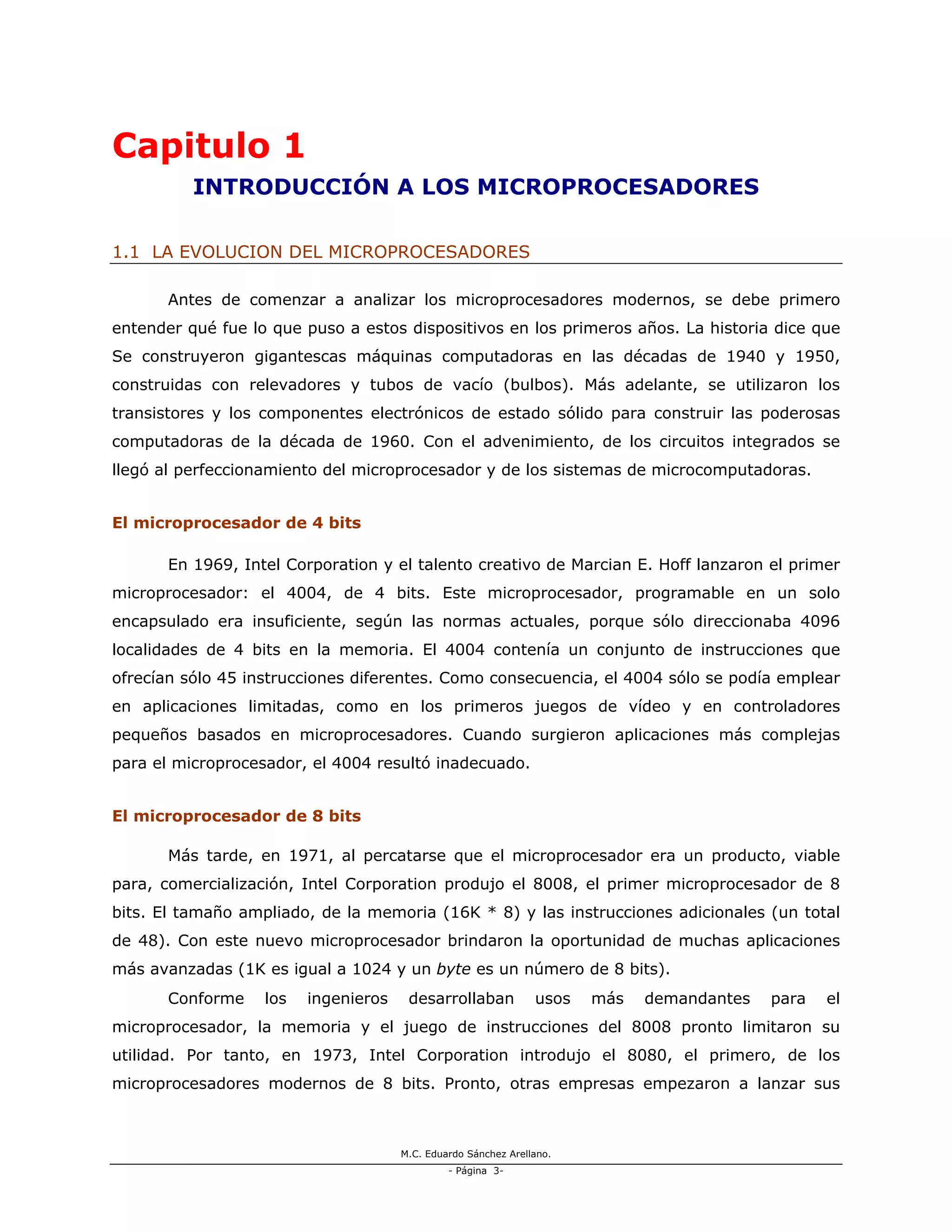

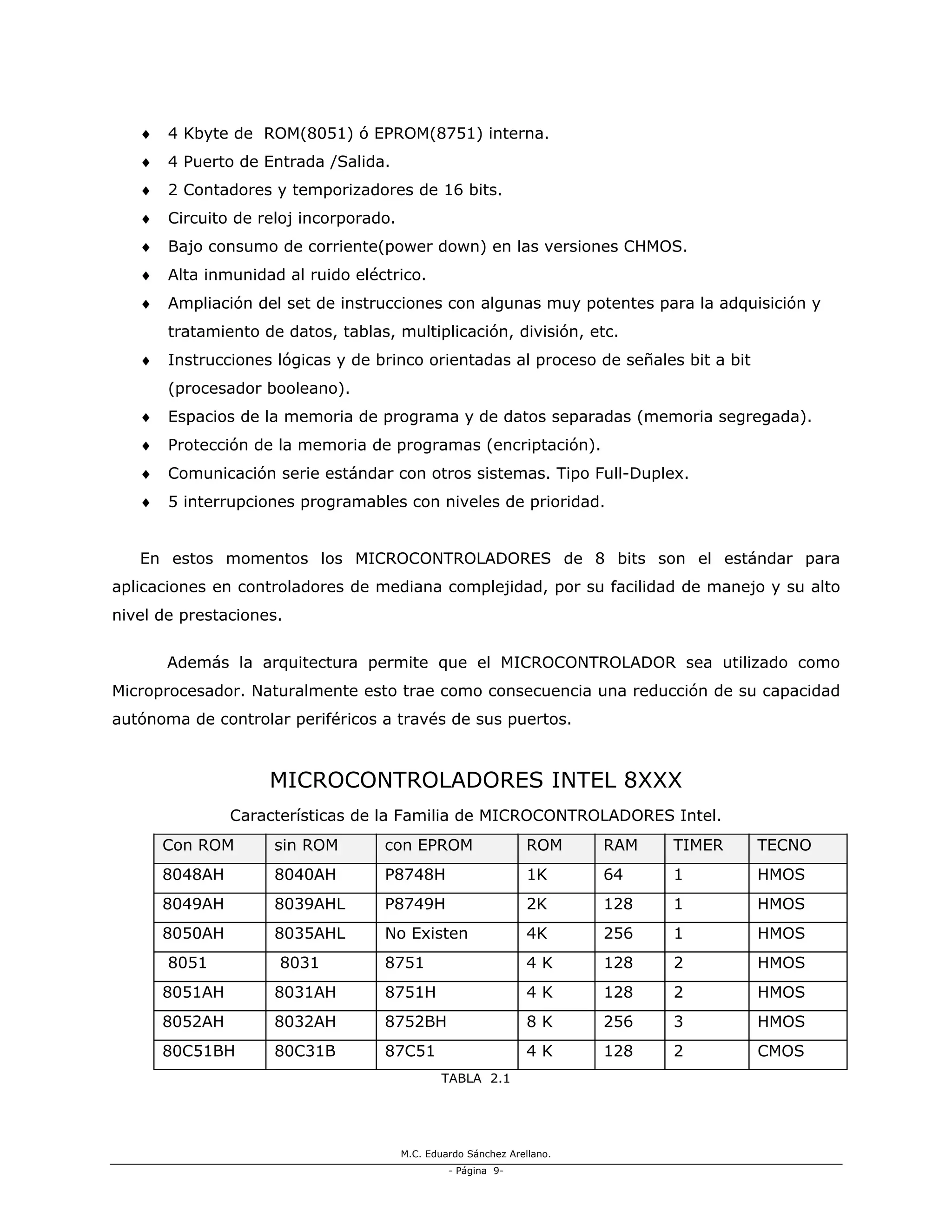

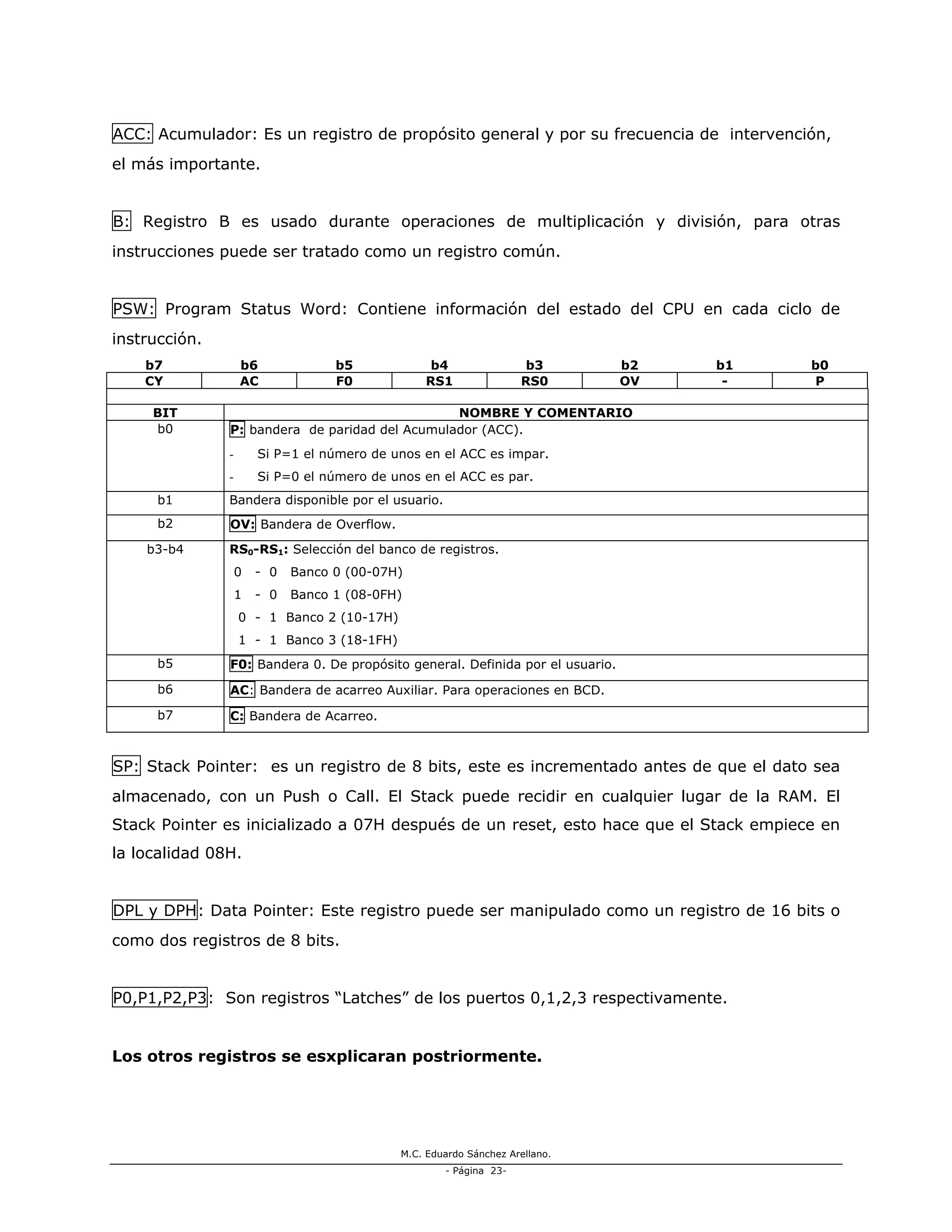

Ejemplo:

A = 5FH

DIV AB B = 0AH

1001 A

1010 0101 1111

0101 B

• La instrucción DA A justa el resultado en binario puro producido por las instrucciones

ADD y ADDC a formato BCD. Esta instrucción no convierte el contenido del acumulador

en BCD, sino que hace ajuste BCD de la suma (resultado), por lo tanto, esta instrucción

debe ir inmediatamente después de la instrucción ADD o ADDC.

Esta es, de forma simplificada, la operación que realiza:

Si [ [(A3-0)> 9] * OR * [(AC) = 1] ]

Entonces (A3-0) (A3-0) + 6

Y si [[(A7-4) > 9] * OR.* [(C)= 1]]

Entonces (A7-4 ) (A7-4) + 6

INSTRUCCIONES LOGICAS

La tabla 4.3 muestra la lista de instrucciones lógicas y los modelos de

direccionamiento que permiten así como los flags afectados.

La duración de ejecución de 1 ó 2 microsegundos considerando un cristal de 12 MHz.

• Las primeras instrucciones corresponden a las operaciones AND, OR, EXOR y NOT.

Ejemplo:

ANL <byte>, # 3 F

Si <byte> = (3A) = 0011 1010

# 3F = 0000 1111

0000 1010 = 0AH

(<byte> se refiere, en este caso, a una posición de memoria.)

Nemónico Operación Modos de direccionamiento

Tiempo de

Flag afectados

Dir Ind Reg Imm

Ejecución

µs C OV AC

ANL A,<byte> A=A.AND.<byte> X X X X 1

ANL <byte>,A <byte>=<byte>.A X 1

ANL <byte>,#data <byte>=<byte>.And. X 2

ORL <byte> A=A.OR. <byte> X X X X 1

ORL <byte>, A <byte>=<byte>.OR.A X 1](https://image.slidesharecdn.com/curso20microcontroladores-1221680878782491-9/75/Curso-de-microcontrolador-MCS51-32-2048.jpg)