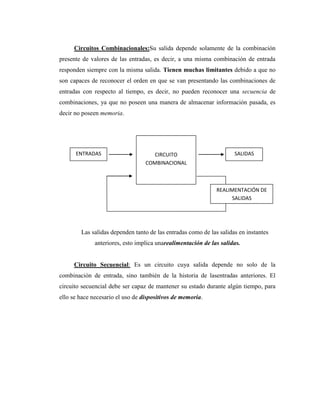

Los circuitos combinacionales producen salidas que dependen solo de las entradas actuales, mientras que los circuitos secuenciales también dependen del estado previo. Los circuitos secuenciales usan elementos de memoria como biestables para almacenar información del estado previo.