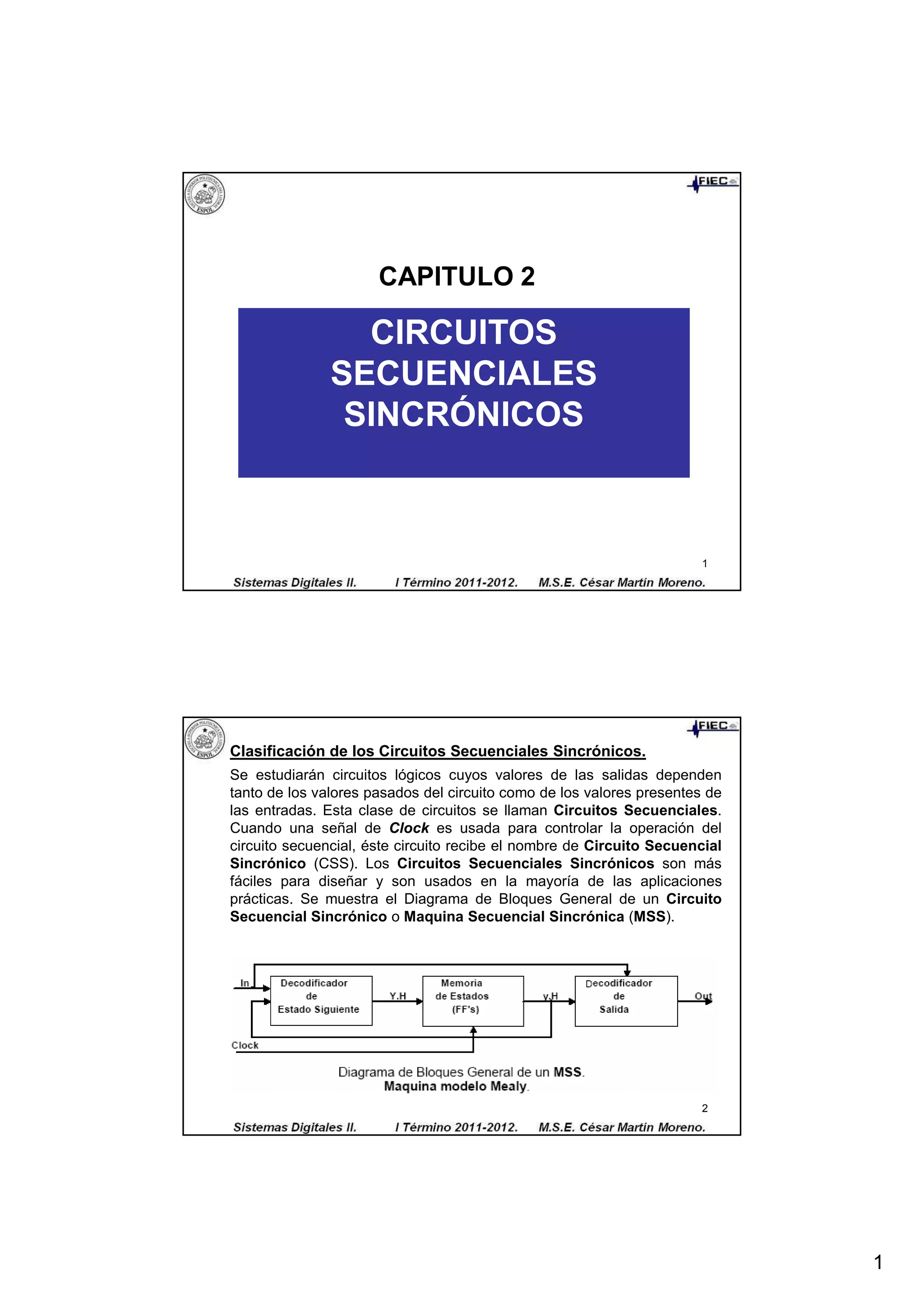

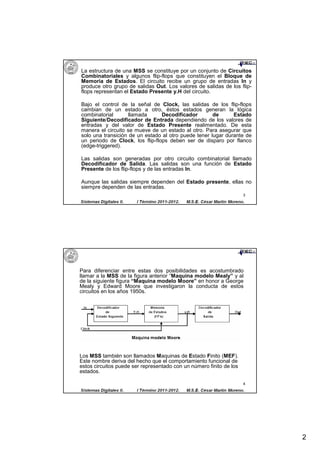

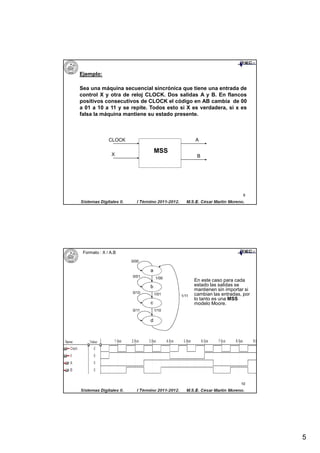

Este documento describe circuitos secuenciales sincrónicos y sus clasificaciones. Explica la estructura básica de una máquina de estado finito sincrónica (MSS) y cómo usa flip-flops y circuitos combinacionales para cambiar entre estados basados en la entrada y la señal de reloj. También introduce diagramas de estados como una herramienta para representar visualmente las transiciones de estado de una MSS.