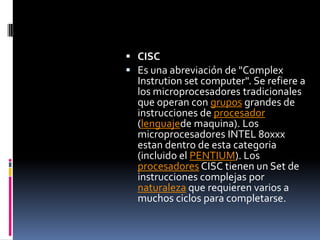

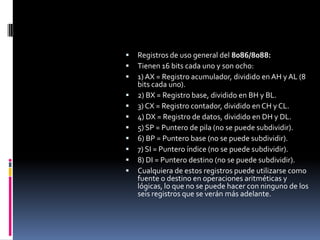

El documento describe la historia y características de los microprocesadores Intel 8086 y 8088. Estos fueron los primeros microprocesadores de 16 bits lanzados por Intel en 1978 y 1979 respectivamente. El documento explica las diferencias entre arquitecturas CISC y RISC, y proporciona detalles sobre los registros, unidades y buses de datos internos de los microprocesadores 8086/8088.