Taller adc - resuelto

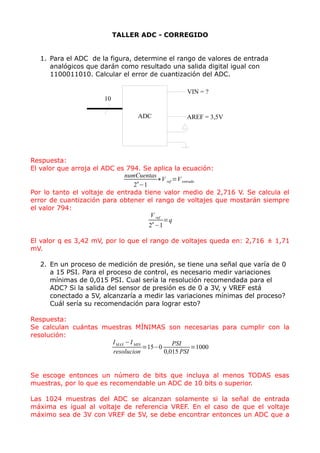

- 1. TALLER ADC - CORREGIDO 1. Para el ADC de la figura, determine el rango de valores de entrada analógicos que darán como resultado una salida digital igual con 1100011010. Calcular el error de cuantización del ADC. Respuesta: El valor que arroja el ADC es 794. Se aplica la ecuación: numCuentas 2 n −1 ∗V ref =Ventrada Por lo tanto el voltaje de entrada tiene valor medio de 2,716 V. Se calcula el error de cuantización para obtener el rango de voltajes que mostarán siempre el valor 794: V ref 2 n −1 =q El valor q es 3,42 mV, por lo que el rango de voltajes queda en: 2,716 ± 1,71 mV. 2. En un proceso de medición de presión, se tiene una señal que varía de 0 a 15 PSI. Para el proceso de control, es necesario medir variaciones mínimas de 0,015 PSI. Cual sería la resolución recomendada para el ADC? Si la salida del sensor de presión es de 0 a 3V, y VREF está conectado a 5V, alcanzaría a medir las variaciones mínimas del proceso? Cuál sería su recomendación para lograr esto? Respuesta: Se calculan cuántas muestras MÍNIMAS son necesarias para cumplir con la resolución: IMAX −I MIN resolucion =15−0 PSI 0,015 PSI =1000 Se escoge entonces un número de bits que incluya al menos TODAS esas muestras, por lo que es recomendable un ADC de 10 bits o superior. Las 1024 muestras del ADC se alcanzan solamente si la señal de entrada máxima es igual al voltaje de referencia VREF. En el caso de que el voltaje máximo sea de 3V con VREF de 5V, se debe encontrar entonces un ADC que a ADC 10 AREF = 3,5V VIN = ?

- 2. 3/5 del rango obtenga las 1000 muestras necesarias para cumplir con la resolución. El valor de 3/5 sale simplemente de VINMAX / VREF. Se puede hacer esto entonces por iteración: Para n = 11, se obtienen 1228 muestras a 3V, por lo que es suficiente un ADC de 11 bits o mayor para esta aplicación. También se puede aplicar la ecuación: numCuentas 2 n −1 ∗V ref =V entrada 1000 2 n −1 ∗5=3 1000= 3 5 (2 n −1) 5000 3 −1=2 n log2( 5000 3 −1)=n log2( 4997 3 )=n log2(4997)−log2(3)=n Se hace cambio de base de logaritmo: ln(4997) ln(2) − ln(3) ln(2) =n Asi, nos da un valor de n = 10.7, que puede ser aproximado a 11. 3. Teniendo dos ADC disponibles para la selección, de diferente fabricante, con resolución de 10 bits c/u, calcule el SNR teórico. Si cada fabricante de los ADC le facilita el SNR real, para el primero de 55 dB y el segundo de 58 dB, cuál seleccionaría? Cuál es el ENOB de cada ADC? Si el proceso en donde se va a utilizar el ADC requiere un paso mínimo de 4 mV, cuál ADC de éstos le serviría? Respuesta Se aplica la ecuación SNR = 6,02xn + 1,76. de esta manera se obtiene un SNR en decibeles de 61,96 dB. Esta es la diferencia entre la potencia de entrada y el ruido de cuantización. Entre más alto el SNR menos afecta el ruido a la señal de entrada. Los valores de SNR del fabricante son efectivamente menores, porque además del ruido de cuantización existen otros ruidos presentes. Se escogería el dispositivo que ofrece el más alto SNR. El ENOB es el número efectivo de bits del ADC, y se calcula con la misma ecuación del SNR pero despejando para n, donde n en este caso es ENOB:ENOB = (SNR – 1,76) / 6,02. De esta manera se obtiene para el dispositivo de SNR = 55dB un ENOB de 8,84 bits, y para el dispositivo con SNR = 58 dB un ENOB de 9,3 bits. Si el paso mínimo o intervalo de cuantización requerido para el ADC es de 4 mV, se puede calcular el intervalo a partir del ENOB:

- 3. 5V 2 8,84 −1 =10,9mV 5V 2 9,3 −1 =7,9mV Ninguno de estos dos ADC serviría. 4. Para un proceso de medición de corriente en un motor, que tiene a la salida del sensor de corriente una razón de cambio de 0,5 mV / ms, se utiliza un conversor ADC de 10 bits, cuyo tiempo de conversión es de 10 ms. Evalúe si es necesario utilizar un circuito S/H y dé la explicación. Respuesta En el tiempo de conversión, el cambio en la señal de entrada debe ser menor al intervalo de cuantización. Se calcula por lo tanto el intervalo de cuantización: V ref 2 n −1 =q= 5V 1023 =4,88mV Entonces, en los 10 ms que se demora el ADC en realizar la conversión, la señal no puede variar más de 4,88mV. En este caso la señal varía más que el intervalo q: 0,5 mV/ms * 10 ms = 5 mV. De esta manera SI se hace necesario utilizar un circuito S/H. 5. Se ha seleccionado un ADC de 10 bits para la conversión de un sensor de temperatura en un proceso. El rango de temperaturas de interés va desde los 0ºC hasta los 100ºC. El sensor de temperatura arroja un valor analógico de 0V a 2.5V en este rango. Asuma que VREF = 5V. Responda las siguientes preguntas: 1. Cuál es el mínimo cambio de voltaje teórico necesario para que el ADC se incremente en un bit? 2. Cuál es el error de cuantización de este sensor? 3. Cuál es, aproximadamente, la cantidad real de muestras que se logra para este proceso? Está utilizando el alcance completo del ADC? 4. Qué procedimiento debería realizar para aprovechar el rango completo del ADC? Respuesta 1. Para el primer punto se calcula el intervalo de cuantización, que al ser VREF de 5V ya sabemos que entonces q = 4,88 mV. 2. El error de cuantización es la mitad del intervalo de cuantización: 2,44 mV. 3. Ya que la señal de entrada llega sólo hasta 2.5V, la máxima lectura en cuentas será aproximadamente la mitad de cuentas del ADC: 511 cuentas. Obviamente no se aprovecha todo el rango del ADC. 4. Para aprovechar el rango completo se pueden hacer dos cosas:

- 4. 1. Amplificar la señal ya sea con la ganancia G interna del ADC (si éste incluye una ganancia de 2) o amplificarla externamente. 2. Cambiar el VREF a 2.5V. 6. El conversor A/D de 8 bits, unipolar, de aproximaciones sucesivas Harris ADC0802LCN presenta un error total de ±½ LSB. La frecuencia de reloj es de 640 Khz. El voltaje de referencia es de 2.5V y se requieren 62 ciclos de reloj para realizar una conversión. 1. ¿Cual es el incremento de voltaje teórico requerido para hacer cambiar el BIT menos significativo? 2. Una vez se tiene un dato digital. ¿Cuál seria la expresión matemática para indicar el voltaje presente en las entradas? 3. Cuál es el error de cuantización? 4. ¿Cual es el máximo número de muestras por segundo que se pueden digitalizar con este dispositivo? 5. Determine la velocidad máxima del cambio de señal en la entrada para hacer innecesaria la presencia de un dispositivo de muestreo y retención. 6. Si se sabe que la señal de entrada varía como máximo a razón de 1 V/seg. ¿Cuál seria la frecuencia de reloj mínima que se podría utilizar? Respuesta Se calcula el intervalo de cuantización : 1. 2.5V 2 8 −1 =9,8mV 2. Se utiliza la ecuación de número de cuentas del ADC: 3. 4. numCuentas=255⋅ V entrada 2,5 =102⋅V entrada 5. El error de cuantización es la mitad del intervalo de cuantización: 4,9 mV. 6. Se calcula cuánto dura la digitalización de una muestra: Si se requieren 62 ciclos de reloj, y cada ciclo tiene una duración de 1 / 640kHz (1,5625 us), entonces cada digitalización requiere 96,875 us. Se calcula entonces la frecuencia o 1 / 96,875 us (10,322 kHz). Quiere decir que se pueden digitalizar hasta 10.322 muestras por segundo. 7. La variación de la entrada debe ser de máximo 9,8 mV. Se calcula entonces cuánto tiempo le toma a la señal de entrada alcanzar este voltaje: 9,8mV =1V/ seg⋅t 9,8 1000 =t=9,8ms Por lo tanto, el mínimo tiempo debe ser de 9,8 ms, y en frecuencia equivale a 102 Hz aprox. 7. Se cuenta con un sólo ADC para un proceso que requiere medir 15

- 5. variables analógicas. Cuál multiplexor escogería usted para este proceso? Si el ADC requiere 10 us para la conversión de una muestra, cual sería la frecuencia real de muestreo para cada señal conectada? Cuál sería la máxima frecuencia de estas señales para poder ser medidas por el ADC? Respuesta 1. Se elige un multiplexor de 16 canales. 2. El tiempo de conversión se alarga en 15 veces, por lo tanto cada señal demora 150 us, (10us por cada señal), por lo que la frecuencia es de 6,666 kHz. 3. Para calcular la máxima frecuencia de la señal, basta con calcular cuál es el máximo cambio permitido en las señales durante los 10 us de conversión, que resulta ser el intervalo de cuantización. 2. Topologías 1. Se tiene un conversor ADC de 8 bits tipo rampa, que trabaja en un rango de 0 a 5V. El máximo retardo de este ADC es de 100 ms, y la rampa aumenta a una rata de 0,05V/ms. Si la entrada a medir está en 3,4 V, cuál es la salida del ADC? Cuánto demora esta conversión? Repetir el ejercicio para 390 mV. Respuesta Se aplica la conocida ecuación del ADC: 3,4 / 5 * 255= 173 cuentas. La conversión demora: 3,4/5*100 ms = 68 ms. Se aplican las mismas ecuaciones para 390 mV. 2. Se tiene un conversor ADC de 10 bits, tipo FLASH (Paralelo). El voltaje de referencia es de 4V. Cuántos comparadores son necesarios en la implementación de este ADC? Si la sensibilidad esperada para el proceso debe ser de 1 mV, serviría este ADC? En caso negativo, cuál sería la resolución del ADC idóneo para esta aplicación? Cuantos comparadores adicionales se requerirían para su implementación? Respuesta Ya que es necesario comparar la señal 1023 veces, se requiere este mismo número de comparadores. La sensibilidad se puede calcula a partir del intervalo de cuantización: 4/1023 = 3,9 mV. Este ADC no serviría. Se requeriría un ADC de al menos 12 bits. Como se requieren 4095 comparadores, entonces se requieren 4095-1023 comparadores adicionales.