Sistema psk & qpsk

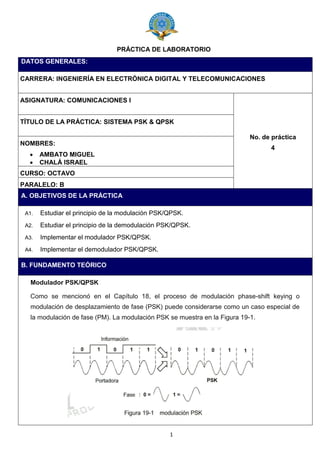

- 1. 1 PRÁCTICA DE LABORATORIO DATOS GENERALES: CARRERA: INGENIERÍA EN ELECTRÓNICA DIGITAL Y TELECOMUNICACIONES ASIGNATURA: COMUNICACIONES I No. de práctica 4 TÍTULO DE LA PRÁCTICA: SISTEMA PSK & QPSK NOMBRES: AMBATO MIGUEL CHALÁ ISRAEL CURSO: OCTAVO PARALELO: B A. OBJETIVOS DE LA PRÁCTICA A1. Estudiar el principio de la modulación PSK/QPSK. A2. Estudiar el principio de la demodulación PSK/QPSK. A3. Implementar el modulador PSK/QPSK. A4. Implementar el demodulador PSK/QPSK. B. FUNDAMENTO TEÓRICO Modulador PSK/QPSK Como se mencionó en el Capítulo 18, el proceso de modulación phase-shift keying o modulación de desplazamiento de fase (PSK) puede considerarse como un caso especial de la modulación de fase (PM). La modulación PSK se muestra en la Figura 19-1.

- 2. 2 En la Figura 19-1, la señal de portadora es una onda sinusoidal con amplitud y frecuencia fija, la señal moduladora es la información binaria. Si la información de entrada es un bajo (0), la señal portadora mantiene su fase. Si la información de entrada es un alto (1), la portadora invierte su fase por 180 grados. Señales senoidales en donde existe un corrimiento relativo de fase de 180 grados entre ellas se les conocen como señales antipolares. Este tipo de desplazamiento de fase se conoce como PSK (BPSK) o inversión de fase (PRK). Así como el BPSK, este esquema de modulación se caracteriza por el hecho de que la información está contenida en la fase de la onda transmitida. En particular, en PSK cuaternaria (QPSK), la fase de la portadora toma solamente uno de los cuatro valores espaciadas equitativamente, tales como, 0º, 90º, 180º, y 270º. Cada valor posible de la fase corresponde a un par único de bits llamado un dibit. Por ejemplo, se puede escoger el juego de valores de fase para representar los códigos de Gray de di bits: 00, 01, 11, y 10. Las formas de onda típica dela modulación QPSK están mostradas en la Figura 19-2. Nótese que el juego de fase de PSK y QPSK mencionado anteriormente es una posible opción. Los otros posibles corrimientos de fase de las señales PSK y QPSK se muestran en la Tabla 19-1.

- 3. 3 La Figura 19-3 muestra un sistema de comunicación PSK/QPSK. El modulador modula la señal portadora con la información de entrada y produce una señal modulada PSK o QPSK. La señal modulada es transmitida a través de un medio de transmisión, tal como aire, y fibra óptica, a la entrada del demodulador. El demodulador recibe la señal PSK o QPSK transmitida y luego reconstruye el dato de información original. La Figura 19-4 muestra los bloques funcionales de un modulador PSK/QPSK. El generador de señal portadora provee una portadora (onda sinusoidal) a la red de conmutación de fase y una onda cuadrada a un circuito de temporización. La red de conmutación de fase provee cuatro salidas (0º, 90º, 180º, 270º) a las entradas del selector de datos. La salida X del selector de datos está determinada por las entradas de selección A y B. Existen cuatro casos: 1. Si BA=00 (Q1 =Q0=low), X=X0, la señal con corrimiento de fase 0º. 2. Si BA=11 (Q1=Q0=high), X=X3, la señal con corrimiento de fase180º. 3. Si BA=01 (Q1=1ow, Q0=high), X=X1, la señal con corrimiento de fase 90º. 4. Si BA=10 (Q1 =high, Q0=low), X=X2, la señal con corrimiento de fase 270º. El circuito de temporización recibe la onda cuadrada (fc) de la salida del generador de señal de portadora y produce dos salidas: fe a la entrada de control de carga y la señal 2fc (doble de la

- 4. 4 frecuencia portadora) a la entrada de reloj del registro de control, así como el generador de ciclo de sincronización. Estas dos señales de fc y 2fc y la velocidad de transmisión (medido en bits por segundo, bps) de la información digital de entrada son usadas para determinar si el modulador opera en modo PSK binario o QPSK binario. Existen tres casos posibles: a. Velocidad de transmisión = fc y no se genera ciclo de sincronización En este caso, la velocidad de transmisión es igual a la frecuencia portadora fc y la frecuencia del reloj es el doble de la frecuencia portadora 2fc. Un bit del juego dato digital es cargado en el registro de control dos veces. Las salidas 00-01 del registro de control son por consiguiente iguales, 00 o 11. La salida X del selector de datos es la señal XO o X3. Este sistema opera en modo PSK. b. Velocidad de transmisión = 2fc y no se genera ciclo de sincronización En este caso, la velocidad de transmisión y la frecuencia del reloj son iguales al doble de la frecuencia portadora, 2fc. Dos bits del juego de datos son cargados en el registro de control cada ciclo de portadora. Las salidas del registro de control 00-01 pueden estar en 00, 01, 11, o1 O. Este sistema por consiguiente opera en modo OPSK. c. Velocidad de transmisión= fc o 2fc, y se genera ciclo de sincronización Si se requiere un ciclo de sincronización, el1 circuito de control de ciclo de sincronización producirá una señal de control para controlar el dato de salida del registro de corrimiento de control, y luego se presenta una señal de ciclo de sincronización a la salida del modulador. En este experimento se usa el formato del ciclo de sincronización mostrado en la Figura 19-5. Esta señal de ciclo de sincronización es diferente de las señales moduladas PSK/OPSK mostradas en las Figuras 19-1 y 19-2. La señal de ciclo de sincronización puede identificarse por el detector de ciclo de sincronización en el demodulador PSK/OPSK y puede observarse como una palabra de identificación. Demodulador PSK/QPSK

- 5. 5 Existe muchos métodos y circuitos usados para reconstruir la información (señal moduladora) de la señal modulada PSK/OPSK. En un demodulador PSK/OPSK típico, se requiere un circuito PLL para reconstruir la señal de reloj usado en el modulador. La Figura 19-6 muestra el diagrama de bloques del demodulador PSK/QPSK. La señal de entrada PSK/QPSK es amplificada por el amplificador 1 y luego rectificado por el rectificador de onda completa. El pulso del rectificador sirve de entrada al detector de fase en el PLL. Esta señal se usa para reconstruir la señal de reloj. La Figura 19-7 muestra el dato de salida del demodulador que es recuperado de la señal PSK/QPSK recibida. De la Figura 19-6, varias frecuencias de reloj son producidas por el PLL y el contador de división por N. Estas señales de reloj son usadas para reconstruir el dato de información y para convertir la señal de sincronización al dato de ciclo de sincronización.

- 6. 6 La conversión del ciclo de sincronización se muestra en la Figura 19-8. La palabra de dato de ciclo de sincronización convertida es 0111. Cuando el detector de ciclo de sincronización recibe esta palabra de dato, se presenta un bajo para indicar la detección del ciclo de sincronización. Descripción del Circuito Practico 1. Modulador PSK/QPSK La Figura 19-9 muestra el diagrama esquemático del modulador PSK/QPSK. El generador de forma de onda de precisión chip ICL8038 sirve como el generador de portadora que produce ondas sinusoidales por cuadradas. La frecuencia del generador de portadora está determinada por las resistencias de temporización externas R2-R3 y el condensador C2 y es aproximadamente 7.1 KHz. Los pines 7 y 8 están interconectados para que el generador opere en modo VCO. La señal sinusoidal generada está conectada a las entradas de la red de conmutación de fase que consta de dos amplificadores no inversores (U2a y U2d) y dos amplificadores inversores (U2b y U2c). Esta red de corrimiento de fase provee cuatro corrimientos de fase 0°, 90º, 270º, y180º a las entradas de datos XO, X1, X2, y X3 del selector de datos (U3), respectivamente. La salida del selector de datos está determinada por el estado de las entradas de selección A y B. Una vez que se selecciona la salida, la señal modulada PSK/QPSK es amplificada por el amplificador no inversor U8. El potenciómetro VR5 se usa para controlar la amplitud de salida de la señal modulada PSK/QPSK. La onda cuadrada presente en el pin 9 de U1 está conectada a la entrada del circuito de temporización para generar una señal con una frecuencia 2fc doble de la frecuencia portadora por la red de duplicación de frecuencia constituido por U4b, U4c, y U5a y componentes asociados R21, R22, C6, C7. La señal 2fc está conectada a las entradas del reloj del registro de corrimiento U7 y el contador binario de 4-bit U6a. La señal de salida del contador en 00 está

- 7. 7 conectada a los inversores U4f y U4d y al pin 1 de U7 (entrada de carga). La frecuencia de esta señal es fe. La señal moduladora (información digital) está conectada a la entrada DATA (pin 2) del registro de corrimiento de control U7. Las salidas 00-01 del registro de corrimiento y la señal en TP6 pasan a través de una compuerta XOR, y luego conectado a las entradas de selección A y B del selector de datos. Los contadores binarios U6a y U6b se usan para determinar la generación de un ciclo de sincronización. La frecuencia de reloj del contador binario U6a es 2fc. La salida 01 de U6a está conectada a la entrada de reloj de U6b, tal que la frecuencia de reloj es fc/2 y la frecuencia de 03 en U6b es fc/32. El ciclo de sincronización se genera solamente por la mitad de la duración de 1<; 1 señal de salida de 03 o sea fc/16.

- 8. 8

- 9. 9 2.) Demodulador PSK/QPSK La Figura 19-10 muestra el diagrama esquemático del demodulador PSK/QPSK. El amplificador U1d recibe y amplifica la señal modulada PSK/QPSK para compensar las pérdidas y mejorar la distorsión causada en la línea de transmisión. El rectificador de onda completa, constituido por amplificadores operacionales U1 c-U1 b y los diodos D1-D4, transforma la señal PSK/OPSK recibida a una señal con ciclos positivos, la cual posteriormente a la entrada del detector de fase en el PLL (U2). La señal VCO out (32fc) sirve como el generador de los pulsos de reloj para el contador de división por N. El contador produce dos frecuencias 4fc y 2fc en las salidas 02 y 03, respectivamente. La señal PSK/QPSK amplificada en la terminal de salida de U1 d está conectada a la entrada del amplificador U 1 a. U 1 a convierte la señal PSK/QPSK a una señal de pulso digital como se muestra en la Figura19-7. Esta señal digital en TP5 pasa a través de unos inversores para levantar la señal U3e y U3f y luego conectados a las entradas J y K* de U4. El detector de ciclo de sincronización contiene un registro de 4 etapas (U4) y una compuerta NANO de cuatro entradas (U5b). La frecuencia del reloj del registro es 2fc. El pulso de reinicio generado por la red (R21, C9, U3d) se usa para reiniciar las salidas del registro Q0-Q3. El dato digital en TP5 está conectado a las entradas J y K*. Cuando se recibe 1:1n ciclo de sincronización, la salidas del registro Q3-Q0 es 0111,y la salida (TP13) de la compuerta NANO de 4 entradas U5b presenta un bajo para indicar la detección de un ciclo de sincronización. Durante TP13 en bajo, la salida de la compuerta NANO U8c está en alto, por consiguiente la salida del demodulador esta inhibido. Para los otros juegos de salida de Q0-Q3, TP13 está en alto. El dato digital en TP5 se envía también a la entrada DATA del registro de corrimiento U7. La frecuencia del reloj de U7 y lJ6b es 4fc, mientras que la velocidad de transmisión del dato de entrada digital es igual a fe o 2fc. Las frecuencias de las salidas Q1 y Q2 del contador (U6b) son fe y fc/2, respectivamente. La salida 01 está conectada a la entrada de carga del registro U9 y a la terminal RX CLK OUT. El contador es reiniciado ya sea cuando se detecta un ciclo de sincronización (TP13=0, CR=1) o cuando la salida de Q2 está en alto (Q2=1, CR=1). La salida del dato de modulado en las salidas de Q2-Q3 de U7 está controlados por la lógica de control (compuertas NANO U8a, b, e, d). Si no se detecta el ciclo de sincronización (TP13=1), el dato de modulado puede enviarse a la terminal DATA OUT. Si se detecta un ciclo de sincronización (TP13=0), el dato es bloqueado por la lógica de control.

- 10. 10

- 11. 11 C. LISTADO DE MATERIALES O HERRAMIENTAS C1. Modulo KL-96001 C2. Modulo KL-94006 C3. Modulo KL-94007 C4. Osciloscopio C5. 2 Puntas de prueba osciloscopio C6. Cable de Energía entre Módulos C7. 2 Jumpers D. INSTRUCCIONES PARA REALIZAR LA PRÁCTICA Experimento 19-1 Medición y Ajuste A. Medición y Ajuste del KL-94006 D1. Aplique las tensiones de suministro de alimentación +12V, -12V, y +5V requeridas al Modulador PSK/QPSK en el Modulo KL-94006 mostrado en la Figura 19-9. D2. Usando el osciloscopio, mida y registre las formas de onda y frecuencias en los puntos de prueba TP1, TP2, y TP3 en la Tabla 19-2. D3. Conecte CH1 IN del osciloscopio a TP3 y CH2 IN a TP4. Mida y registre las formas de onda y frecuencias en la Tabla 19-3. Fije la amplitud de la señal en TP4 a 1Vpp ajustando VR1 y observe la diferencia de fase entre estas dos formas de onda. D4. Conecte el CH1 IN del osciloscopio a TP3 y CH2 IN a TP6.Mida y registre las formas de onda y frecuencias en la Tabla19-3. Fije la amplitud de la señal en TP6 a 2Vpp ajustando VR2y observe la diferencia de fase entre estas dos formas de onda. D5. Conecte el CH1 IN del osciloscopio a TP3 y CH2 IN a TP5.Mida y registre las formas de onda y frecuencias en la Tabla19-3. Fije la amplitud de la señal en TP5 a 3Vpp ajustando VR3y observe la diferencia de fase entre estas dos formas de onda. D6. Conecte el CH1 IN del osciloscopio a TP3 y CH2 IN a TP7.Mida y registre las formas de onda y frecuencias en la Tabla19-3. Fije la amplitud de la señal en TP7 a 3Vpp ajustando VR4y observe la diferencia de fase entre estas dos formas de onda. D7. Conecte una onda cuadrada de 500Hz, nivel TTL a la terminal Digital DATAIN. D8. Conecte el CH1 IN del osciloscopio a PSK/QPSK OUT. Mida la forma de onda y fije la amplitud de salida a 10 Vpp ajustando VR5 y registre el resultado en la Tabla 19-4. (Nota: La frecuencia no puede medirse en este caso.) D9. Apague la fuente de alimentación.

- 12. 12 D10. Conecte PSK/QPSK OUT del Modulo KL-94006 a PSK/QPSK INPUT del Modulo KL-94007. D11. Conecte las fuentes de alimentación requeridos en ambos B. Medición y Ajuste del KL-94007 D12. Conecte el CH1 IN del osciloscopio a TP4. Mida y fije las tensiones cd a -5Vdc ajustando VR2. Úsese un DVM (Voltímetro Digital) para obtener una lectura exacta de la tensión de alimentación. D13. Conecte el CH1 IN del osciloscopio a TP1. Mida la forma de onda y frecuencia y fije la amplitud a 5Vpp ajustando VR1. Registre el resultado en la Tabla 19-5. D14. Conecte el CH1 IN del osciloscopio a TP1. Mida la forma de onda y frecuencia y fije la frecuencia a 32fc ajustando VR3. Registre el resultado en la Tabla 19-6. Si la frecuencia portadora es 8KHz, la frecuencia de la señal en TP11 deberá ser 256KHz. D15. Conecte CH1 IN del osciloscopio a DATAOUT. Mida y registre la forma de onda y frecuencia en la Tabla 19-7. La forma de onda en DATA OUT deberá ser la señal digital demodulada, 500Hz. Si no es así, usted puede girar ligeramente VR1 o apagar y encender nuevamente la fuente de alimentación. D16. Conecte el CH1 IN del osciloscopio a la terminal RX CLK OUT. Mida y registre la forma de onda y frecuencia en la Tabla 19-7. La forma de onda en RX CLK OUT debe ser la señal portadora recuperada. Si no es así, usted puede ajustar ligeramente VR1 o apagar y encender nuevamente la fuente de alimentación. D17. Apague la fuente de alimentación. Experimento19-2 Modulador PSK &QPSK A. Medición de 2fc (KL-94006) D18. Conecte una señal digital de 500Hz, nivel TTL en Digital DATAIN. D19. Conecte el CH1 IN del osciloscopio a TP12 y CH2 IN a TP13.Mida y registre las formas de onda y frecuencias en la Tabla 19-8. Compare la diferencia de fase entre estas dos formas de onda. D20. Conecte el CH1 IN del osciloscopio a TP15. Mida y registre la forma de onda y frecuencia en la Tabla 19-8. La frecuencia debe ser el doble de la frecuencia portadora, 2fc. B. Medición del Ciclo de sincronización D21. Mida y registre las formas de onda y frecuencias en los puntos de prueba listados en la Tabla 19-9. C. Medición del Registro de Corrimiento de Control D22. Conecte el CH1 IN del osciloscopio a TP10 y CH2 IN a TP11.Mida y registre las formas de onda y frecuencias en la Tabla19-10. D23. Repita el paso D22 para de frecuencias de señales digitales de 100Hz y 1kHz a Digital DATAIN.

- 13. 13 D24. Restaure la frecuencia de la señal digital de 500Hz. D. Medición de la señal Modulada PSK/QPSK D25. Conecte el CH1 IN del osciloscopio a PSK/QPSK OUT. Mida y registre la forma de onda con varios settings de TIME/DIV en la Tabla 19-11. Experimento 19-3 Demodulador PSK &QPSK A. Medición del Detector de Ciclo de Sincronización (Modulo KL-94007) D26. Conecte una onda cuadrada de 500Hz, nivel TTL a la terminal Digital DATA IN. D27. Fije la tensión CD en TP4 a los valores listados en la Tabla 19-12. Usando el osciloscopio, mida y registre las formas de onda y frecuencias en TP5, TP6, TP7, y TP13 para cada valor fijado en la Tabla 19-12. D28. Fije la tensión CD en TP4 a -5V. B. Medición del Rectificador de Onda Completa D29. Conecte una onda cuadrada de nivel TIL con frecuencias, listadas en la Tabla 19-13, a la terminal Digital DATA IN. Usando el osciloscopio, mida y registre las formas de onda y frecuencias en TP2, TP3, y TP9 para cada una de las frecuencias listadas en la Tabla 19-13. D30. Conecte una onda cuadrada de 500Hz, nivel TTL a la terminal Digital DATA IN. C. Medición de 32fc, 4fc y 2fc D31. Mida la frecuencia en TP11 para obtener una frecuencia igual a 32fc mediante el ajuste de VR3. Mida y registre las formas de onda y frecuencias en TP11, TP8, y TP12 en la Tabla 19- 14. D. Medición del Registro de Corrimiento D32. Mida y registre las formas de onda y frecuencias en TP7, TP12, TP14, U7 Q2, y U7 Q3 en la Tabla 19-15. E. Medición de la Salida del Demodulador D33. Mida y registre las formas de onda y frecuencias en DATA OUT y RX CLK OUT en la Tabla 19- 16. D34. Repita el paso D33 para las frecuencias de Digital DATA IN de 100Hz y 1 kHz. E. RESULTADOS OBTENIDOS E1. F. RESULTADOS OBTENIDOS

- 14. 14 Tabla 19.2 Medición y ajuste Módulo KL-94006 Punto de Prueba Frecuencia Forma de Onda TP1 17,24 KHz TP2 7,24 KHz TP3 7,24 KHz Tabla 19.3 Medición y ajuste Módulo KL-94006

- 15. 15 Punto de Prueb a Forma de Onda y frecuencia TP3 Frecuencia 7,23 KHz TP4 Frecuencia 7,24 KHz TP3 Y TP4 TP5 Frecuencia 7,23 KHz TP3 Y TP5

- 16. 16 TP6 Frecuencia 7,23 KHz TP3 Y TP6 TP7 Frecuencia 7,23 KHz TP3 Y TP7 Tabla 19.4 Medición y ajuste Módulo KL-94006 Punto de Prueba Forma de Onda

- 17. 17 PSK/QPSK OUT Tabla 19.5 Medición y ajuste Módulo KL-94007 Punto de Prueba Forma de Onda y frecuencia TP1

- 18. 18 Tabla 19.6 Medición y ajuste Módulo KL-94007 Punto de Prueba Forma de Onda y frecuencia TP11 Tabla 19.7 Medición y ajuste Módulo KL-94007 Punto de Prueba Forma de Onda DATA OUT

- 19. 19 RX CLK OUT Tabla 19.8 Medición 2fc Módulo KL-94006 Punto de Prueba Forma de Onda y frecuencia TP12 (CH1) FRECUENCIA 7,23 KHz TP13 (CH2) FRECUENCIA 7,23 KHz

- 20. 20 TP15 FRECUENCIA 14,475 KHz Tabla 19.9 Medición de ciclo de sincronización

- 21. 21 Punto de Prueba Forma de Onda y frecuencia TP15 TP16 TP8

- 22. 22 TP17 Tabla 19.10 Medición de registro de corrimiento Frecuenci a Digital DATA IN Punto de pruebas CH1=TP10 CH2:TP11 500Hz 100Hz

- 23. 23 1kHz Tabla 19.11 Medición de la señal modulada PSK/QPSK Osciloscopio TIME/DIV Forma de Onda PSK/QPSK OUT 2.5ms 1ms

- 24. 24 500µs 250µs 100µs Tabla 19.12 Medición del Detector de Ciclo de sincronización (KL-94007) Tensión DC en TP4 Puntos de prueba TP5 TP6

- 25. 25 -5VDC TP7 TP13 -3VDC TP5 TP6 TP7 TP13

- 26. 26 -1VDC TP5 TP6 TP7 TP13 0VDC TP5 TP6

- 27. 27 TP7 TP13 +3VDC TP5 TP6 TP7 TP13

- 28. 28 Tabla 19.13 Medición de Rectificador de Onda Completa Frecuencia Digital DATA IN (KL-94006) Puntos de prueba TP2 500Hz TP3

- 31. 31 Tabla 19.14 Medición de 32fc, 4fc y 2fc Punto de Prueba Forma de Onda TP11 (32fc) TP8 (2fc)

- 32. 32 TP12 (4fc) Tabla 19.15 Medición de registro de corrimiento Puntos de Prueba Forma de Onda y frecuencia TP12 TP7

- 33. 33 TP14 U7 Q2 U7 Q3 Tabla 19.16 Medición del Detector de Ciclo de sincronización (KL-94007) Frecuencia Digital DATA IN (KL-94006) Puntos de prueba DATA OUT RX CLK OUT

- 35. 35 H. CONCLUSIONES Y RECOMENDACIONES CONCLUSIONES: En un sistema de comunicación PSK/QPSK, el modulador modula la señal portadora con la información de entrada y produce una señal modulada PSK o QPSK El cambio de fase de 0-180° ocurre cada vez que sucede un flanco de subida o de bajada de la señal portadora. El parámetro que se modifica de la portadora es el ángulo de fase el cual cambia cada vez que hay un flanco de subida o de bajada en la señal moduladora. El tren de pulsos enviados a una frecuencia mayor hace que la modulada cambie de fase a una frecuencia mayor. RECOMENDACIONES: Se recomienda revisar la teoría, ya que brinda las bases teóricas necesarias para poder puntualizar algunas de las posibles formas de implementar un modulador y demodulador PSK. Se recomienda de forma opcional, previo al desarrollo de la práctica realizar un estudio para saber con qué nos vamos a encontrar, haciendo uso de la herramienta Simulink del paquete de simulación MatLab. I. BIBLIOGRAFÍA J. ANEXOS 1. ¿Por qué la señal modulada PSK/QPSK posee cuatro corrimientos distintos de fase? Debido a que la señal portadora toma 4 valores posibles, se producen 4 desplazamientos de fase que proveerán 4 fases distintas, correspondiendo cada uno de ellos a un dibit diferente. 2. ¿Cómo los corrimientos de fase de 90º y 270º son producidos por una red RC, la desviación de fase puede ocurrir debido a la variación de los valores de los componentes? Cuando la señal modulante es una sinusoide de frecuencia única, es evidente, que el ángulo de fase de la portadora varía de su valor no modulada bajo un enfoque de sinusoidal. La máxima desviación de fase se llama índice de modulación.

- 36. 36