Electrónica digital: capitulo 7 Autómatas finitos parte 2

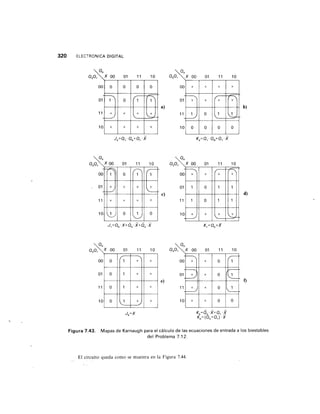

- 1. 00 01 1 1 _ 1 0 x 0 0 0 1 1 1 1 0 0 0 0 0 ¡ 0 Í f-'') " l x [ , . t'-,1 X X X X J r = Q r ' O o + Q r 'X 320 E L E C T R O N I C A D I G I T A L Q"o Q,Q ara,, oro, arQ', Ko:Ó, x+a.,.8 K o = ( Q , + A ) ' X parael cálculode lasecuacionesde entradaa los biestables del Problema7.12. a) c) a, e) Figura7.43. Jo:X M a p a s d e K a r n a u g h El circuito queda como K r : O . , ' O n + A , , ' * { r oo 01 1 1 1 0 x o o 0 1 1 1 1 0 n0 r;-) I " J X X I [ , . X X X 1/ 0 U 0 J r : Q o 'r ¡ Q r . X + Ó r ' X K',:Ao+X o o. x o o 0 1 1 1 1 0 00 01 11 1 0 0 I ' l X 0 1 X X 0 1 X X 0 1_) X se muestraen la Fieura 7.44.

- 2. AUTOMATASFINITOS 321 7404 Entradade control pares/impares Entrada impulsos ck , Figura 7.44. Circuitoresultadodel Problema7.12. 7.13. Diseñar un contador de 0 a 7 que mediante una señal de control sólo cuente hasta 3 (de 0 a 3). Solución: De acuerdocon el enunciadodel problema, si el circuito seimplementa utilizando la teoría de autómatas hnitos tendrá ocho estados sobre los que se puede evolucionar de acuerdo con el diagramade flujos de la Figura 1.45. Figura 7.45. Diagramade flujos del contadorcontrolado(Problema7.13) La Tabla 7.31es la de estados, que corresponde con el diagramade flujos de la Figura7.45. J aH o.+ i I b C Salida 747 t " 0 )C, K , . 0 lul101

- 3. 322 ELECTRONICA DIGITAL Tabla 7.31. Tablade estadosdel Problema7.13 Al haberseelegidoel modelo de Moore para la implementacióndel sistema,y para simplificarel cir- cuito de salida,se codifican los estadosinternos de manera que coincidan con las salidas,por tanto: 1o.__-- 000 1¡ .-' 011 Iu --r I l0 1r - 001 1o--------+ 100 It - lll 12----------------' 010 1s----------------' 101 En estecasosedecideimplementarel circuito con biestabletipo J-K, por lo que sepuede realizarla Tabla 7.32donde ya se han sustituidolos estadosinternospor los códigos asignados. Tabla 7.32. Tablade transiciones del Problema7.13 Estadopresente X Estadofuturo A B C Io I^ I1 Il I2 I2 I. I" I4 I^ Is I.f I. I6 I1 [1 0 I 0 I 0 I 0 I 0 I 0 I 0 I 0 I Il I1 I2 I2 I.-) I" -t Io I4 Io I.) Io I6 Io I1 Io Io 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 1 0 0 1 0 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1 Estadopresente Qzot Qto Qoo X Estadofuturo Qrrrn rtQrt*Qo<r*, K2 J2 K1 Jl Ko Jo Salidas A B C 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 1 0 0 1 0 1 1 0 1 1 1 0 1 1 0 l l l 1 1 1 0 I 0 I 0 1 0 I 0 1 0 I 0 1 0 I 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 0 0 0 1 0 0 0 0 0 1 0 1 0 0 0 1 1 0 0 0 0 l l l 0 0 0 0 0 0 0 x 0 x 0 x 0 x 0 x 0 x 0 x 1 x x l x 0 x 1 x 0 x 1 x 0 x 1 x 1 0 x 0 x 1 x l x x 0 x 0 x l x l 0 x 0 x 0 x 1 x x 1 x 0 x l x 1 1 x 1 x x l x l l x l x x l x 1 0 x l x x 1 x l 0 x l x x l x l 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 1 0 0 1 0 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1

- 4. Los mapas de Karnaugh para deducir las ecuaciones salidas,son los que se muestranen la Figura 7.46. AUTOMATASFINITOS 323 de interconexión de los biestablesJ-K y las QrA J r : O ' , ' A o ' X ara ara Jo:Qt+X Ko:1 Figura 7.46. Mapas de Karnaughparael cálculode lasfuncionesde entradade los biestables d e l P r o b l e m a 7 . 1 3 . ao o2 b) a) Q, d) c) a ( o o 0 1 1 1 1 0 00 01 1 1 1 0 0 0 0 0 0 0 r,-) 0 X t_, X X X 0 ( o o 0 1 1 1 t o 00 01 1 1 1 0 ¡ X F X e ¡ 1 0 1_ :) j 0 0 I K z : X + O 1 ' A o " 00 01 1 1 1 0 ( o o 0 1 1 1 1 0 0 0 l f ' I X (_ , . l X x 0 0 t , 0 J . , : A o . X + O o . Ó , o 00 01 1 1 1 0 I x o o 0 1 1 1 1 0 X X F ¡ 0 0 1 1 r-) 0 1 f " ) X X l l x K . , : O o + A r ' Y o 00 01 11 1 0 00 01 1 1 1 0 (: X 1 1 l I X 1 1 1 1 L 1 I ) J o : O r + Y

- 5. 324 control C* Entrada imPulsos Figura7.47. 7.14. Diseñar un contador síncronode ello biestablesdel tipo ./-K. Solución: El diagrama de flujosdel E L E C T R O N I C A D I G I T A L Finalmente,el circuito queda como se muestra en la Figura 7.47. Resultado módulo 6 circuitoesel del Problema 7.13. con salida de arrastre (Carry) utilizando para quesemuestra enla Figura7.28. x--o x:1 x:o X=O X=1 de un contador de Problema7.14. X:O Figura 7.48. Diagrama de flujos módulo 6 con salida de arrastredel

- 6. AUTOMATASFINITOS 325 La tabla de estadosde estesistemaserála que se muestraen la Tabla7.33. Tabla 7.33. Tabla de estadosdel Problema7.14 Como el contador tieneseisestadosinternos,para poder codificarlossenecesitanal menostres bits. Además, como se ha tenido la precaución de utilizar el modelo de Moore, si hacemoscoincidir los estadosinternos con la salida las funcionesde éstascoincidirán con las salidasde los biestables,por tanto se realiza la siguienteasignaciónde estados: 1o-----.--------- 000 1¡.+ 011 1r .-.-----------* 001 14----------------+ 100 12---------------- 010 1. ---------+ 101 Por tanto, la Tabla 7.34es la de transicionesdel contador de módulo 6, utilizando biestablesdel tipo "/-K activos por flanco de bajada. Tabla 7.34. Tablade transiciones del Problema7.14. Aplicando el método de Karnaugh se pueden deducir las funciones de entrada y salida de los biestables(Fig. 7.a9). Estado actual X Estado futuro Carry C Salida contador A B C Io Io Il I1 I2 I2 I"-l I.J I4 I4 Is Is 0 I 0 I 0 I 0 I 0 I 0 I Io Ir Ir I2 I2 I^ -l I.J I4 I4 I.) Is Io 0 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 1 0 0 1 0 1 1 0 1 Estado actual Qzo Qto¡ Quvt - Estadofuturo Qze+t)Qt+t Qot,*rt J2 Kz Jr Kr Ko Jo Salida A B C CR 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 r 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 0 0 0 0 x 0 x 0 x 1 x x 0 x 1 0 x l x x 0 x l 0 x 0 x I X I X 1 X X I X I X I 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 0 0 0 0 0 I

- 7. O.o, 00 326 E L E C T R O N I C A D I G I T A L J , : Ó r ' O o O " C 1 0 0 0 1 1 1 1 0 0 I 0 0 0 0 0 C l C ^ : Q o ' Q , Figura 7.49. Mapas de Karnaughpara la obtenciónde lasfuncionesde entraday salida de los biestables (problemaj.14). o c) s) arQ, o o 0 1 ,o., 00 01 1 1 1 0 0 X X 0 Cl X 0 ora', ¡ O o 0 1 ,O,, 0 0 0 1 1 1 1 0 I ' X (_ 1 X Ko=1

- 8. Por tanto, el circuito queda tal y como se muestra en la AUTOMATAS FINITOS Figura 7.50. 327 I Salida CR L . - . Entrada Figura 7.50. Resultado del Problema7.14. 7.15. Diseñar un contador síncrono de módulo 10 con salida de carry utilizando para ello biestablestipo 7. Solución: El diagramade flujosdel contadorde módulo 10corresponde al que semuestraen la Fisura7.5l. Clock

- 9. 328 E L E C T R O N I C A D I G I T A L /"/s=0000 X:O x:1 c:0 Figura 7.51. Diagramade flujos de X:O x:1 /./S=0110 c:0 X:O un contador de décadas con salida de carry (Pro- b l e m a7 . 1 5 ) . X=O X : 1 X:O X : 1 Por tanto, la Tabla ra7.51,en la queya se u I y, por tanto, se ha 7.35serála tabla de estados ha tenidoen cuentaque para eliminado de la tabla. correspondienteal diagrama de flujos de la Figu- pasarde un estadoa otro la entradaX ha de estar Tabla 7.35. Tablade estadosdel Problema7.15 i./s=0010 /3/s=001 1 / ,/S=01 11 x=o /./S=0100 X:O Estadoactual Estado futuro Salida A B C D Carry CR Io I.l I2 I"-) I1 Is I6 I1 I8 Ie I1 I2 I--l I1 I.J I6 I1 I,ó Ie Io 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 r 0 0 0 1 0 1 0 r l 0 0 1 t l 1 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 I

- 10. AUTOMATASFINITOS 329 Como hay diez estados distintos, harán falta al menos cuatro dígitos para poder codificarlos. Además.como hemos utilizado el modelo de Moqre, se hacen coincidir los estadosinternos con los valoresde las salidas,de tal manera que en cada momento la salida coincida con el estadointerno del biestablecorrespondientey, por tanto, se ahorra el circuito de salida. Además,teniendoen cuentaque seutilizan biestablesdel tipo 7",la tabla de transicionesesla que se muestraen la Tabla 7.36. Tabla 7.36. Tablade transiciones del Problema7.15 Para obtener las funcionesde entrada y salida de los biestablesseempleael metodo de Karnaugh (Figura7.52). n , 0 0 0 1 1 1 1 0 00 01 1 ' l 1 0 0 0 X 0 0 0 C_ l 0 C *-., [ , J I X ¡ 0 0 X T " : A r ' Q o + A r ' Q . , 'Q o 3 a ) . 0 0 0 1 1 1 1 0 00 01 1 1 1 0 0 0 X 0 0 0 x U C 1 X l 0 0 X X T r : A ' , ' Q o o, b) a) Figura 7.52. Mapas de Karnaughpara deducir las funciones de entraday salida de los biestables del Problema7.15. Estado actual Qx¡ Qz@ Qu,¡ Qr<¡ Estado futuro Qsu+tl Qz(,*rl Qt(t+rt Qn(+t To Tr T2 T3 Carry CR 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 l 0 l 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 l 0 0 l 0 0 0 0 0 0 0 1 0 0 1 1 0 0 0 1 0 1 1 1 0 0 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 1 1 0 0 1 0 0 0 0 o 0 0 0 0 I

- 11. o , 0 0 0 1 1 1 1 0 00 01 1 1 1 0 0 0 X 0 n-¡ X 0 L :) 0 0 X T.,=Ó".oo 3 3 0 E L E C - R o N l c A D t G t r A L o)€ Figura 7.52. Mapas de Karnaughpara deducir las funciones de entraday salidade los biestablesdel Problema 7.15. (Continuación). Por tanto, el circuito seráel de la Fieura 7.53. c) o1 d) e) o o 00 01 1 1 1 0 2. 00 01 11 '10 f- 1 l 1 X 1 I 1 1 1 X X I I l 1 1 X I To:1 a" 2 , 0 0 0 1 1 1 1 0 00 01 1 1 1 0 0 0 X 0 0 0 f- 1 l I 0 0 :_ x l 0 0 X X C : Q r . A o

- 12. AUTOMATAS FINITOS 331 Figura 7.53. Resultado del Problema7.15. 7.16. Utilizando el conceptode autómatasfinitos,diseñarun dado electrónicocon biestables -/-K y la lógica necesaria. Solución: La implementación de un dado se puede simular sin más que diseñar un contador de seis estados,que correspondencon las seiscarasque tiene un dado, donde la entrada a contar es un tren de impulsosgeneradopor un multivibrador de una frecuenciaelevada(del orden de I KHz por ejemplo)y que se cuenta o no depen<liendo cleque se pulse o no el interruptor de tirada. Segúnlo expuestohastael momento,nuestrodiagramade estadosseráel de la Figura7.54,enel qu. ufu...en lás salidasdel 1 al 6 en binario. Se ha optado por utilizar un autómata de Moore para poa.i hacer coincidir los estadosinternos con las salidasy de esta forma simplificar el diseño.

- 13. 332 E L E C T R O N I C A D I G I T A L X:O x=0 X:O X : 1 x=1 x:1 l , l 0 1 o Figura 7.54. Diagramade estadosdel dado electrónico(Problema7.16). La tabla de estadosde acuerdocon el diagramade estadoses la Tabla 7.37. Tabla 7.37. Tablade estadosdel Problema7.16 Estado presente X Estado futuro Salidas s, s, s, Io I,) I1 I1 I2 I2 I" I.J I4 I1 Is I.J 0 I 0 I 0 I 0 I 0 I 0 1 Io I1 I1 I2 I2 I- I" I4 I4 I.) I.) Io 0 0 1 0 0 1 0 1 0 0 r 0 0 l r 0 r 1 r 0 0 1 0 0 r 0 l 1 0 1 1 1 0 I l 0 Seguidamente se hace la asignaciónde estados;en el caso que nos ocupa haremoscoincidir los estadosinternos con las salidas,para simplifrcar más rápidamente éstas,ya que, de esta manera, al simplificarlas coincidencon los estadosinternosdel autómata y, por tanto, con las salidasQ" de los biestables. Luego la asignaciónserála siguiente: 1o--..-.-- 001 /r - 010 1 z - 0 1 1 13--------, 100 Ia---- l0l Is --------+ 110 Sustituyendo estacodificaciónen la tabla de estadosy ampliandoéstacon la tabla de transiciones de los biestables ./-K se obtienela Tabla 7.38.

- 14. AUTOMATAS FINITOS Tabla 7.38. Tablade transiciones del Problema7.16 333 Teniendoen cuentaque la variaciónde un estadointerno a otro serealizasiempreque X sea l, se puedenobtener las ecuaciones de entrada de los biestables teniendoen cuenta sólo Qt, Qt Y Qo, Y haciendoentrar el tren de impulsospor la señalde reloj. Con ello, los mapasde Karnaugh para las ecuaciones de entradade los biestables son las que se muestranen la Figura 1.55. Figura 7.55. Mapas de Karnaughparael cálculode las ecuaciones de las funcionesde los biestables. Estado presente Qr<,t Qtt¡ Qrut X Estado futuro Qz<t+t¡Qt+tl Qov*rl Salida ü ^tr so K2 J2 Kr Jr Ko Jo 0 0 r 0 0 r 0 1 0 0 1 0 0 l l 0 1 1 1 0 0 1 0 0 1 0 1 1 0 1 1 1 0 1 1 0 0 I 0 1 I 0 I 0 I 0 I 0 I 0 0 1 0 1 0 0 1 0 0 1 1 0 l l 1 0 0 1 0 0 1 0 1 1 0 1 1 1 0 1 1 0 0 0 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 1 0 0 1 0 1 1 0 1 1 1 0 r 1 0 U < 0 x 0 x 0 x 0 x 1 x x 0 x 0 x 0 x 0 x 0 x l 0 x 1 x . x 0 x 0 x 0 x l 0 x 0 x 0 x l x x 0 x l x 0 x l 0 x 1 x x 0 x 1 0 x l x x 0 x l 0 x l x J r : Q ' , ' Q o Kr=Ao+O, 0 1 1 1 I = 1 " o

- 15. 334 E L E C T R O N I C A D I G I T A L L¿s salidas,al haber utilizado el modelo de autómata de Moore y al haber hecho coincidir la codlficacionde los estadosinternos con los de las salidas,coinciden con las e. Por tanto' el circuito, aplicándoleel decodifrcadory el display,queda como se muestraen la Figu- ra 7.56. Figura7.S0. Resultado del problema 7.16. 7'17' Un sistema-sencillo para probar circuitos digitalescombinacionales es tomar un circuito patrón igual al que sequiereprobar, poner a ambostodaslas posiblescombinaciones de las variablesde entrada y comprobar que para cada una de ellasla salidade ambos circuitos coincide,en estecasoel circuito bajo prueba serácorrecto. Si no seproduce coincidenciade salidaspara una combinación de las variablesde entrada, el cirtuito bajo prueba será defectuoso. Basándose en esto,diseñarun sistemaautomáticode pruebade circuitoscombinaciona- les de tres entradascuyo diagrama de bloqueses el ..pr.r.ntado en la Figura 7.57. A B C D E F G B I / R R B B L 1 2 4 8 1 0 I T Jo P^ Ao fmpulsos de clock

- 16. c I R c U I T o 2 c I R C U I T o 1 C I R C U I T O 3 AUTOMATAS FINITOS 335 Figura 7.57. Diagramade bloques del sistemade pruebaspara circuitoscombinacionales. Diseñar los circuitos 1, 2 y 3 cuyasmisionesson las siguientes: Circuito l: Debe poner automáticamente todas las combinaciones de entrada a los circuitosbajo prueba,teniendoen cuentaque la combinación100no debedarsenunca,ya que si esto ocurre el circuito en prueba y el patrón sedestruirían por ser una combinación de proteccióncontra copias. Debe encenderse la lámpara cuando se haya terminado de poner todas las combinacio- nes y mantenerla encendidahasta que se vuelva a dar una señalde inicializacion' por tanto, el circuito del bloque 1 dispondrá de un sistemade inicializacionpara probar otro circuito y que ademásdesactive la lamparilla lr. Circuito 2: Compara las salidasde los dos circuitos. Circuito 3: Seactiva en casode que el circuito no estéen perfectoestadoy permanecerá encendidaaunque cambienlas combinacionesde entrada hastaque seintroduzca una señal de inicialización. Solución: El circuitodelbloqueI tendrásiete estados, puesla combinación deentrada100no deberá darse nuncaya queeneste casosedestruyen loscircuitos. Por ello,el diagrama deflujosdelsistema es el dela Figura7.58. l,l01o 1,1011 lnl101 tul11o Figura 7.58. Diagramade flujosdel generadorde códigos de entradadel Problema7.17'

- 17. 336 ELEcrRoNrcA DrGrrAL La Tabla 7.39es la de estadosque correspondeal diagramade flujos de la Figura 7.58. Tabf a 7.39. Tabla de estadosdel Problema7.17 Estado presente X Estado futuro A B C Io Io Ir I1 I2 I2 I.-t I.-t I4 I4 Is Is I6 I6 0 I 0 I 0 1 0 1 0 I 0 1 0 I Io Il Ir I2 Iz I.-t I.-t I4 I4 Is Is I6 I6 I6 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 l l 0 1 1 1 0 1 1 0 1 I l 0 1 1 0 1 1 1 1 1 1 Por haber sido elegidoel modelo de Moore para la implementacióndel sistema,y para simplificar el circuito de salida, se codihcan los estadosinternos de manera que coincidan con las salidas,por tanto: 1o.-------------' 000 14 --------------- l0l 11----------------' 001 Is --------------- 110 1z --------------- 010 16-"'--"-'-+ lll 1. -------------+ 011 En estecaso se decideimplementar el circuito con biestabletipo J-K, con lo que se puede realizarla Tabla 7.40donde ya se han sustituidolos estadosinternospor los códigosasignados. Tabfa 7.4O. Tablade transiciones del Problema7.17. Estado presente Qzt¡ Qu,¡ Qrr,, X Estado futuro Qztt+t'tQte+t) Qot,*r't K2 J2 Kr Jl Jo Ka Salidas A B C 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 l 0 l 1 0 1 1 1 0 1 1 0 l l l t l 1 0 I 0 I 0 I 0 1 0 I 0 1 0 1 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 1 1 0 1 1 1 0 1 1 0 1 1 1 t t l 1 1 1 0 x 0 x 0 x 0 x 0 x 0 x 0 x l x x 0 x 0 x 0 x 0 x 0 x 0 0 x 0 x 0 x 1 x x 0 x 0 x 0 x l 0 x 1 x x 0 x 0 x 0 x 0 0 x l x x 0 x l 0 x l x x 0 x 0 x 0 x 1 0 x 1 x x 0 x 0 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 l l 0 1 1 l 0 l 1 0 1 1 1 0 1 1 0 1 l l 1 1 1

- 18. AUTOMATASFINITOS 337 de interconexión de los biestablesJ-K y las Los mapas de Karnaugh para deducir las ecuaciones salidasson los que se muestranen la Figura 7.59. 1 2ooo 01 11 10 0 1 0 0 r;)0 X X t l I r l X J . = O . , ' A o Figura 7.59. Mapasde Karnaugh a) d) K ' , = Q o ' 4 , parael cálculo de las funcionesde entradaa los biestables del Problema7.17. El circuito correspondienteal bloque 1 será,por tanto, el de la Figura 7'60' ñ o , o o 0 1 1 1 1 0 0 ,l C l 0 x 0 0 J.,:oo J o : 1 c o o o 0 1 1 1 1 0 0 1 I ¡ 0 X I [ , , j 0 X Ko=Q',

- 19. 338 E L E C T R O N I C A D I G I T A L A lasentradas del circuitode pruebay patrón Figura 7.60. Circuitodel bloque 1 del problema7.1j. El circuito disponede una señalde Resetpara inicializar el sistemaponiendo todas las salidasa 0. La lámpara L, de estecircuito es un diodo Led y se pondrá a I cuando todas las salidassean 1, permaneciendoen esteestado hasta que se active la señalde Reset,ya que el estado 111 es el Iu del diagramade flujos. El circuito 2 puederealizarsecon un comparador del tipo 7485conectado,tal y como semuestraen la Figura 7.61. Figura7.61. Circuito del bloque2 delProblema 7.17. El circuito 3 debe mantener una información hasta que se inicialiceel sistema,para lo cual puede emplearse el circuito de la Figura7.62.Cuando en la entradaAhay un 0 y previamente seha activado Pulsadorde inicialización Circuito patrón AO A 1 4 2 A 3 BO B1 B2 B3 A < B A < B A = 8 A = B A > B A > B Circuito en prueba A la entra bloque 3

- 20. AUTOMATAS FINITOS 339 el pulsador de inicializacion,a la salidade la puerta OR hay un 0. Cuando sepone a 1 la entrada A ala salidade la puerta OR, apareceun 1 que serealimentaa travésde la entrada B, de tal manera que si la entrada A pasaa valer de nuevo 0 la salida de la puerta OR seguirásiendo un 1. Del bloque 2 Figura 7.62. Circuitobloque 3 del Problema7.17. 7.18. Diseñar un circuito secuencial síncronoque dispongade una entrada X sincronizadapor una señalde reloj y una salida S, de tal manera que si por X se introduce un número de cuatro bits comenzandopor el bit de menor peso,a su salidaseobtengael complementoa 2 de dicho número de forma simultáneacon éste.Ademásel circuito deberáquedarpreparado para recibir otro número cuando termine de realizarel complemento del anterior. Solución: El circuito corresponderá a un diagrama de bloques similar al que se muestra en el diagramade bloquesde la Figura7.63, en el que se muestrala entrada X, la salidaS y la entradade sincronismo C,. Figura7.63. Diagrama de bloques delcircuito complementador a 2 (Problema 7.18) Para realizarel complementadoa 2 de un número binario, en primer lugar serealizael complemen- to a 1 d.elnúmero (cambianlos 0 por los 1 y los I por los 0) y seguidamente se le suma l; así por ejemplo: Delpulsador inicialización Circuito complementador a 2

- 21. 340 E L E C T R O N I C A D I G I T A L 0100 _+ 1011 _ r 1 I100- 01t0 -------------- 1001 + 1 ro lo (-- Complemento *- Complemento F- Complemento (- Complemento a l a 2 a l a 2 También, como puede verse, pafa realizar el complemento a 2 de un número binario de forma metódica se puede hacer de la siguientemanera: Empezandopor el bit de menor pesoy desplazándose hacia el de mayor (de derechaa izquierda),si el bit es un 0 se queda como está,y cuando nos encontramoscon el primer 1, éstese queda también como está,pero a partir de estebit en adelantese cambian los 0 por 1 y los 1 por 0. Teniendo en cuenta esto, y sabiendo que los datos están sincronizadospor la señal de reloj, se puede plantear el siguientediagrama de flujos del circuito (Fig. 7.64). Figura 7.64. Diagrama de flujosdel circuitogenerador del complemento a 2 de un número de cuatrobits(Problema 7.18). / o o / ( t 1 t¡ * ( ¡ o o 5 o'/ + t s; + t o t¡ La Tabla 7.41es la de estadoscorrespondiente al diagramade flujos de la Figura7.63.

- 22. AUTOMATAS FINITOS 341 Tabla 7.41. Tablade estadosdel Problema7.18 Estado presente X Estadofuturo Salida ,s Io Io Il Ir I2 I2 I3 I3 IN T, I.) Is I6 I6 0 1 0 I 0 I 0 I 0 I 0 I 0 I I1 I4 I2 Is I3 I6 Io Io I.f I.) I6 I6 Io Io 0 1 0 I 0 I 0 1 I 0 I 0 I 0 Seguidamentesecodifican los cinco estadosinternos del autóm ata, para lo que necesitaremos tres bits. Por tanto, se realizanlas siguientes asignaciones: 1o--+ 000 1¿- 100 1r .------------001 /s ----------------+ 101 1z .-.--.--------- 010 16-+ 110 1. ------------+ 011 En este caso se decide implementar el circuito con biestablesdel tipo J-K, por lo que se puede realizarla Tabla 7.42 dondeya se han sustituidolos estadosinternospor los códigosasignados. Tabla 7.42. Tablade transiciones del Problema7 18 Estado presente Qz<,t Qu,¡ Quot Entradas X Estado futuro Qztt+t¡ Qt(,*t) Qo<t+t¡ J2 K2 Jr Kr Ko Jo Salida .S 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 r r 0 1 1 1 0 0 1 0 0 1 0 1 1 0 1 1 1 0 1 1 0 0 1 0 I 0 I 0 I 0 I 0 1 0 I 0 0 1 1 0 0 0 1 0 1 0 1 0 1 1 1 0 1 0 0 0 0 0 0 1 0 1 1 0 1 1 1 0 r l 0 0 0 0 0 0 0 ( r x 1 x I ' X l x 0 x 1 x 0 x 0 x x 0 x 0 x 0 x 0 x l x l 0 x t.l x l x 0 x x 0 x l x l x 1 0 x 0 x 1 x 1 x x l x 1 1 x 0 x x l x 0 1 x 1 x x l x. 1 1 x 1 x x l x l 0 x 0 x 0 1 0 I 0 I 0 I I 0 I 0 1 0

- 23. 342 ELEcrRoNtcADtctrAL Los mapas de Karnaugh para deducir las ecuacionesde interconexión de los biestables./-K y las salidasson los que se muestranen la Figura 7.65. o r Q 3"" oo 01 11 10 1 00 01 1 1 1 0 Q, Q, o, Q,, a r o Q, O,, a) e) Jo:Qr' Ar+Ar' O.,*Ó,, J o = Q r @ Q . , + Q r . X . , Kr:Q',+Qr+X oo Q r A x 0 0 0 1 1 1 1 0 00 01 1 1 1 0 0 T i) 0 0 k ü 0 1l 0 X (^ t 0 0 t_ s:d. .x+02.X:o,gx Mapas de Karnaughpara la obtención de las funciones de entrada los biestables del circuito (problema7.19). s) Jr=do'r ¡ Ó.,. X: X.1o"+o,¡ 3"xoo K,:Q, 3'xoo J,,=Qo'X + Q". Qo=Qo.1X+ Or¡ 9"roo Kr:Ar+X+go x 0 0 0 1 1 1 1 0 00 01 1 1 1 0 , 0 X (y C 1 X D 0 0 X X o 1 X T} 3't oo Figura7.65. y salidade

- 24. AUTOMATAS FINITOS 343 El circuito queda como se muestra en la Figura 7.66. X Entrada delnúmero de4 bits Figura7.66. Resultado del Problema 7.18. 7.1g. Diseñar un circuito secuencial síncronoque evolucionea partir de un estadoinicial, -/0,de forma que cuando haya acabadode recibir dos unos consecutivos por una líneade entrada X seobt.ngu por una líneade salidaS el complementode los dos bits siguientes que reciba, y al mismoli..npo que los ha recibido. El sistemapermaneceráen un estado final It dando salida cero, hastá que se inicialice de nuevo el sistemamediante una señalde resetexterna. Solución: Como se pide que las salidasde los bits complementadosque llegan despuésde los dos 1 consecutivostienen qu. upu...er al mismo tiempo que se reciben,habrá que desarrollar el autómata por el método de Mealy. El diagramade flujos del sistemapuedeser el que se muestraen la Figura7.67- x:0/s=0 Salida del número de 4 bitsen complemento a 2 C* (Reloj) Figura 7.67. Diagramade flujos del detector y siguientesque reciba generadorde complemento de los dos bits ( P r o b l e m a 7 . 1 9 ) . 7486 ¡ = 1 / S = 0 X=0/S=0 x:1ls:o

- 25. 344 ELEcrRoNrcA DtctrAL La Tabla 7.43es la de estadoscorrespondiente al diagramade flujos de la Figura7.67. Tabla 7.43. Tabla de estadosdel Problema7.19 Estado presente X Estado futuro ^s Io Io IL Ir I2 I2 I3 I3 Il Ir 0 I 0 I 0 I 0 1 0 I I^ Ir Io I2 I3 I3 Ir Ir If If 0 0 0 0 I 0 1 0 0 0 Seguidamente secodificanlos cuatro estadosinternosdel autómafapara lo que necesitaremos tres bits. Por tanto, se realizan las siguientesasignaciones: / o - 0 0 0 / : - 0 1 1 1r - 001 1r -----+ 100 1 z - 0 1 0 En este caso, se decide implementar el circuito con biestablesdel tipo J-K, por lo que se puede realizarla Tabla 7.44 donde ya se han sustituido los estadosinternos por los códigos asignados. Tabla 7.44. Tablade transiciones del Problema 7.19 Los mapas de Karnaugh para deducir las ecuacionesde interconexión de los biestables-/-K y las salidasson los que se muestranen la Figura 7.68. Estado presente Qru', Qru¡ Qnvt Entrada X Estadofuturo Qz<t+tlQIG*D Quu*tt K2 J2 Kl Jr Jo ro Salida .s 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 l l 0 1 1 1 0 0 1 0 0 (, I 0 1 0 I 0 1 0 I 0 0 0 1 0 0 1 0 1 l 1 l 0 0 0 0 0 0 0 0 0 0 0 0 0 0 I I 'l I 0 x 0 x 0 x 0 x 0 x 0 x 1 x l x x 0 x 0 0 x 0 x 0 x l x x 0 x 0 x l x 1 0 x 0 x 0 x l x x l x 1 l x 1 x x l x l U X 0 x 0 0 0 0 I 0 I 0 0 0

- 26. x 0 0 0 1 1 1 1 0 00 01 1 1 1 0 0 0 0 0 0 0 r I X x t¡ t X X X X J r : A r ' Q o oo AUTOMATAS FINITOS 345 Ko:1 Karnaughpara el cálculo de las funciones de entraday salidade los biestables (Problema7.19). a r Q o . a b) a) d) g) Kr=0 K',=Ao J o = O r + O r ' Y o ) 00 01 1 1 1 0 00 01 1 1 1 0 0 0 0 0 I 0 0 Í- r l X X u_ 0 0 X X s:o,'X Figura7.68. Mapasde

- 27. 346 ELECTRONICA DIGITAL El circuito queda como se muestraen la Figura 7.69. Reloj C* X Entradade bits a complementar F i g u r a 7 . 6 9 . R e s u l t a d o d e l P r o b l e m a 7 . 1 9 . 7.20. Se desea realizar el receptor de una cerradura codificada mediante una serie de datos codificadospreviamente(11011).Dicho receptor estará realizad,o mediante un autómata síncronocon una única entradaX por la que lleganlos bits seriey una salidaS que será I cuando se reciba la secuenciadeseada. La secuenciapuede llegar en cualquier momento y una vez que la salida se hace I el circuito retorna a su estadoinicial (Fig. 7.70). ck Figura 7.7O. Diagrama de bloques del detector de secuencia (Problema 7.20). solución: Suponiendoque la señalque llega al receptorseencuentra del sistema,el diagrama de flujos del circuito detectorde la secuencia Figura 7.71. La Tabla 7.45de estadoscorrespondienteal diagrama de flujos de la sincronizadacon el reloj interno 11011 esel que semuestraen la Figura 7.71. 1408 1

- 28. x=0/s:0 x:0/s=0 x = 1IS = 1 x:1Is=1 x:0/s:0 x:0/s:0 ¡ = g / S = 0 AUTOMATAS FINITOS 347 Figura 7.71. Diagramade flujos del circuitodetectorde la secuencia11011 en el Proble- ma 7.20 Tabla 7.45. Tabla de estadosdel Problema7.20 Estado presente X Estadofuturo Salida ,s Io Io I I1 I2 I2 T- -1 I- J I^ I1 0 I 0 I 0 I 0 I 0 I 1,, I1 Io I2 I- I2 Io I4 Io Io 0 0 0 0 0 0 0 0 0 1 A continuaciónsecodifrcanlos cinco estadosinternosdel autómata,para lo que necesitaremos dos bits. Se realizanlas siguientesasignaciones: 1o------.-.-_ 000 1r ----------* 001 /z----------------* 010 En este caso se decide implementar el circuito con biestablesdel tipo J-K, por lo que se puede realizarla Tabla 7.46donde ya se han sustituidolos estadosinternospor los códigosasignados. Tabfa 7.46. Tablade transiciones del Problema7'2O 1¡--.---------011 /o ---------------- 100 Estadopresente Qx¡ Qrr,¡ Qnvt Entradas X Estado futuro Qzr,*tl Qto+t) Qu(*rr Jz K2 Jr Kr Ko Jo Salida X 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 l l 0 1 1 1 0 0 1 0 0 0 1 0 1 0 1 0 I 0 1 0 0 0 0 0 1 0 0 0 0 1 0 0 1 1 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 x 0 x 0 x 0 x 0 x 0 x 0 x 1 x x l x l 0 x 0 x 0 x 1 x x 0 x 0 x l x l 0 x 0 x 0 x l x x 1 x l l x 0 x x l x l 0 x 0 x t, 0 0 0 0 0 0 0 0 I

- 29. 348 ELEcrRoNtcADtGtrAL Los mapas de Karnaugh para deducir las ecuacionesde interconexión de los biestables,/-K y las salidasson los que se muestran en la Figura 7.72. oñ oo 01 11 10 00 01 1 1 1 0 0 0 0 0 0 0 f') 0 X U x X X X J r : A o ' A r ' X oo orÑ a2 a) 00 01 1 1 1 0 d) o, Q, oY oo 01 11 10 00 01 1 1 1 0 0 0 0 0 0 0 0 0 F- ¡ X 0 tL_ ¿ X s : Q r ' X Figura 7.72. Mapas de Karnaughpara la obtención de las funciones de entraday salidadel autómatadel Problema7.2O. ao a2 s) Kr:1 X J r = O o ' X 3"^ K't:Qo on '-- X Jo=Or.A.,'x+a.,.X o" : X 0 0 Ko:1

- 30. AUTOMATAS FINITOS 349 Por tanto, el circuito quedacomo se muestraen la Figural.73. Figura 7.73. Resultado del Problema -1.2O. 7.21. Sedeseadiseñarun circuito secuencialpara implementar una máquina de venta automática de cajasde cerillas.Sesuponeque la cajade cerillascuesta7 ptas.y que sepuedenintroducir monedasde 1 pta. y de 5 ptas. indistintamente y en cualquier orden. El circuito deberá tener dos salidasS, y ^S,las cualestienen las siguientesfunciones: . S,,si la máquina tiene que entregarla caja de cerillas;estasalidaserá 1. . Sz indicará en binario el número de pesetas a devolvercuando se hayan introducido más de 7 ptas. Así, por ejemplo, si habiendo introducido en la máquina la cantidad de 3 ptas. se introduceposteriormente una monedade 5 ptas.;la máquina debedevolver 1 pta.,entregar la cajade cerillasy quedarsea la esperade que sele empiezena introducir nuevasmonedas para adquirir otra caja de cerillas. Solución: En primer lugar se realiza el diagrama de flujos: en el diagrama de la Figura 1.74 el sisnificado de las variableses el sieuiente: o X : I se ha introducido 1 pta. o X : 0 se ha introducido una moneda de 5 ptas. . S, : 0 no dispensacaja de cerillas. . S, : I se dispensauna caja de cerillas. . ,S, : indica el número de pesetasa devolver en binario. (Reloj)

- 31. x:0/s,:1/.s,:01 0 350 DIGITAL A continuación se realiza estados distintosse necesitan. la asignaciónde códigos por los menos,tres bits binariosa los estados para codificarlos. 7.47 correspondientea rnternos.Como hay siete vQ=ooo S,=0 s.=ooo X=015.,= 1/Sr=0'l 0 X:O/S, :1 /Sr=100 {¡s^=tls.- Figura 7'74' Diagramade flujos de la máquina expendedorade calasde cerillasdel pro- b l e m a7 . 2 1 . !=0r", De acuerdocon el diagrama de la Figura 7.74,se puedeescribirla Tabla los estadospor los que pasael autómata finito. Tabla 7.47. Tablade estados del problema 7.21 Estado presente X Estadofuturo ,SI s, Io Io I. Il I2 I2 I.-t I3 I1 I4 I5 I.) I.o I6 0 I 0 I 0 I 0 1 0 I 0 1 0 .l I, Ir I6 I2 I^ T" -t Io I4 Io I.) Io I6 Io Io 0 0 0 0 I 0 1 I 0 1 0 I 0 I I 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 1 0 0 0 0 0 1o- 000 1, - 001 1 z - 0 1 0 1¡ -_ 0ll

- 32. 14+ 100 Is ---------------- 101 /ó -----' 110 En estemomento se decideque la implementación se sustituyendo los estados de codificación en la tabla de excitación de los biestables./-K se obtiene la Tabla 7.48. AUTOMATAS FINITOS 351 hará con biestables del tipo J-K, por tanto, estadosy ampliando ésta con la tabla de Tabfa 7.48. Tabla de transicionesdel Problema7.21 Los mapas de Karnaugh para deducir las ecuacionesde interconexión de los biestables.I-K y las salidasson los que se muestranen la Figura 7.75. Q, Q'' o, a) Figura 7.75. Mapas de Karnaughparael cálculode las funcionesde entraday salidade los biestables del Problema7.21. Estadopresente Qzu¡ Qu,¡ Qot¡ X Estadofuturo Qz(t+tQto+t) Qot*tl s, Salida A B C K2 J2 Jr Kl ro Ko 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 1 0 0 l 0 l 1 0 1 1 1 0 1 1 0 0 I 0 1 0 1 0 I 0 I 0 1 0 I 1 0 1 0 0 1 1 1 0 0 1 0 0 0 0 0 1 1 0 0 0 1 0 0 0 0 0 1 0 1 0 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 I 0 I 0 1 0 I 0 1 I 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 1 0 0 0 0 0 1 x 0 x 1 x 0 x 0 x 0 x 0 x 1 x x l x 0 x l x 0 x 1 x l 0 x 0 x 1 x 1 x x l x 0 x l x l 0 x 0 x 0 x 1 x x 1 x 1 l x 1 x x l x l 0 x l x x l x l 0 x 1 x x 1 x 1 0 x 0 x 3""00 J r = 4 . , ' X + O 1 ' O o ' X o^ ,:Jg 00 01 1 1 1 0 Kr:O''+X

- 33. o^l ñ x I 0 0 352 E L E C T R O N I C A D I G I T A L Q, Q, o2 J r : Q o . X + A z : A o J o : A r ' A r + Q r ' X + A t ' X = -..- - -- J o : A r ' O r + Q ; X ' Q . , ' X = O r Q ,+ A r ' X + 4 , , ' X = 4 . , ' a r ' a r 'X ' o . , ' X 0 x 0 0 0 1 1 1 1 0 00 01 1 1 1 0 0 0 0 0 0 0 0 0 0 0 X _D 0 0 C S a : O . ' O . , ' X K . , : O o ¡ O r + X : A o ' Q " ' X o X 0 0 0 1 1 1 1 0 I 00 01 1 1 1 0 0 0 0 0 0 0 0 n 0 0 X g 0 0 0 U a,4,, a, o, a r Q e) a. a, h) s) s,, s, a r Q S " : O , ' O . , ' X S c : o , ' O o ' * + A ' , ' Q o ' X Sc:Oo'X' lAr+Q,¡ Figura 7.75. Mapas de Karnaughparael cálculode las funcionesde entraday salida biestablesdel Problema 7.21. (Continuación)' a" r - X 0 0 oS_Joo 01 11- 10 00 01 1 1 1 0 C 1 x l 3 0 k-_ " J X 0 0 x X 0 C " l X 3""oo Ko:1 ox oo 01 11 10 00 01 1 1 1 0 0 0 0 0 i) 0 0 r 1 1 X ü 0 0 tL ,ñ oo 01 11 10 00 01 1 1 1 0 0 0 0 0 0 0 0 0 3 0 X C 0 0 0 0 S t : A . ' A . , ' * de los

- 34. AUTOMATAS FINITOS 353 Por tanto, el circuito quedacomo se muestraen la FiguraT.l6 Figura7.76. Resultado del Problema 7.21. 7.22. Un circuito de alarma que controla la entrada de una puerta lo realizamedianteun circuito electrónico que sigueel diagrama de bloques de la frgura Reset Figura 7.77. Diagrama de bloques del sistema de alarma del Problema 7.22. El bloque I esun dispositivo que proporciona un impulso de corto tiempo cada vez que se abre o cierra una puerta (sesupone que estebloque está ya realizado). Circuito de ataque a dispositivo acústico- luminoso

- 35. 354 ELEcrRoNlcA DlGlrAL El bloque -Bes un circuito de control que detectaque se ha abierto por segundavez la puerta, ¿ando una salida de valor 1 y quedando bloqueada hasta que sevuelvea inicializar con una entrada de Resetel sistema. Por su parte,el circuito de ataque al dispositivo rizador de tal forma que si en un tiempo prudencial se pone en marcha el sistemaacústico-luminoso. Realizar el bloque B empleando para ello biestables del tipo "r-K. Solución: En estaocasiónserealizarámediantelos modelosde Mealy y Moore pudiéndosecomparar de esta manera los dos. El diagrama de flujos para el modelo de Moore es el que se muestra en la Fisura 7.78. X=0 X:1 Figura 7.78. Diagramade flujos del sistemade alarmade acuerdocon el modelo de Moore del Problema7.22. Como se puede apreciar en estemodelo, las salidasdel circuito se han dibujado en el interior del círculo correspondienteal estado interno indicando de esta manera que mientras que el autómata se encuentra en un estado determinado la salida que se obtiene es la que correspondea dicho estado independientemente del valor de X, y se seguiráobteniendo dicho valor hasta que el autómata no se encuentreen el estado siguiente. El diagramade flujos para el modelo de Mealy es el que semuestraen la Figura7.79. x:0/s:0 x:0/s:0 x:1/s:0 x:1/s:0 x=1IS:1 x:1/s:0 acústico-luminoso incorpora un tempo- no seha activado el Resetdel bloque ^B x:1 | / s =1 x:01 flujos del sistemade alarmade acuerdo del Problema7.22. con el modelo de Mealy Figura 7.79. Diagramade

- 36. AUTOMATAS FINITOS 355 En este caso las salidas se representanfuera del círculo que representael estado interno del autómata indicándosede estaforma que en el momento en que aparecela señalX cambia la salidaaun cuando se encuentreel autómata en el estado de transición. La tabla de estadospara estosdos modelosserálaTabla 7.49. Tabla 7.49. Tablade estados del Problema 7'22 Estadopresente X Estadofuturo SalidaMoore SalidaMealy Io Io Il Ir I2 I2 I.-t I" 0 1 0 I 0 1 (.1 1 Io Il I 1 I2 I2 I" -t I. I" 0 0 0 0 0 0 I I 0 0 0 0 0 1 1 1 Como hay cuatro estados,para poder codificarlosharán falta dos bits, realizandola siguiente asignaciónde estados: 10--.- 00 1r ---------------' 0l I, -- -' l0 1. ---+ 1I Sustituyendo estascodihcaciones en la tabla de estadosy ampliandoéstacon la tabla de excitación de los biestables ./-K se obtienela Tabla 7.50. Tabla 7.50. Tablade transiciones del Problema 7'22 Estado presente Qto Qoo X Estado futuro Qtu+tt Qo6+r¡ Salida Moore Salida Mealy Jl Kr Jo Ko 0 0 0 0 I I I .l 0 0 I I 0 0 .l 1 0 1 0 1 0 I 0 I 0 0 0 I 1 1 1 1 0 1 1 0 0 I I 1 0 0 0 0 0 0 1 1 0 0 0 0 0 I 1 I 0 0 0 1 X X X X X X X 0 0 0 0 0 1 X X 0 I X X X X 0 1 X 0 0

- 37. ELECTRONICA DIGITAL Como se puede apreciar,tanto en la Tabla 7.50como en los dos diagramasde estados(Moore y Mealy) para pasar de un estadoa otro siemprese cumple que X : 1,mientras que cuando X : 0 no hay transición a otro estado, por tanto, en los mapas de Karnaugh para obtener las funciones de interconexión se puede eliminar la variable X ya que ésta será siempre I y se deberá conectar la entrada X a la entrada de reloj que en cada momento es un impulso generadopor el bloque ,4. De acuerdo con esto los mapas de Karnaugh de interconexión y de las salidas serán los que se muestran en la figura 7.80. S . M o o r e : O r . A o S . M e a l y - A r ' X + O , . O o b) a) d) oo Figura 7.2O. Mapas de Karnaughpara la obtención de los biestablesdel Problema las funciones de entraday salida de 7.22. Por tanto, el circuito correspondienteal bloque B será el representadotanto la salida del modelo de Mealv como la del de la Figura 7.81,en el que se han modelo de Moore. o, ' ) 'l 1 l 0 1 0 r;) X t l (v Jr=Oo o 0 1 1 0 1 x X 0 0 K,,:O o o, 0 1 0 1 el X 0 Ko=Q', 0 1 x 00 01 1 1 1 0 0 0 0 0 0 e!) D

- 38. AUTOMATAS FINITOS 357 S a l i d a Mealy Salida Moore Entrada al bloque I X 7476 Figura 7.81. Circuitocorrespondiente al bloqueI del diagramade bloquesde la Figura7.77' PROBLEMAS PROPUESTOS 7.23. Si la al circuito correspondienteal Figura 7.82b)por la entrada diagrama de flujos de la Figura7.82a) se le introduce una señalcomo X sincronizada con la señalde reloj, ¿quéseñalse obtiene a la salida? V Entrada de reloj X:0/S=0 x=0/s:0 Figura7.82. Enunciado del Problema 7.23. q x x=1ls:o x=0/s:0 x=0/s=0 ¿ b )

- 39. 358 ELECTRoNtcA DtGtrAL Solución: V Entrada de reloj S a l i d a 7.24. Obtener la tabla Solución: Figura7.83. Resultado del Problema 7.23. de transición deldiagrama deflujosde la Figura7.82a) Tabla7.51. Resultado delProblema 7.24. Estado actual Entrada X Estado futuro Salida Io Io Il I1 I2 I2 I3 I1 I4 I4 0 1 0 1 0 I 0 1 0 1 Io Il I1 I2 I2 I1 I3 I4 I4 I ,., 0 0 0 0 0 0 0 0 0 1 7.25. Si en el circuito correspondiente al por la entrada X sincronizadacon diagramade flujos de la Figura 7.84a)se introducela señal7.84b, la señalde reloj, ¿quéseñalse obtienea la salidadel circuito? x=0 S e ñ a l de reloj X:O Figura7.84. Enunciadodel Problema7.25.

- 40. Solución: S a l i d a Figura 7.85. Resultado del problema7'25' 7.26. Obtener la tabla de estadosdel diagramade flujos de la Figural'84a)' Solución: Tabla7.52. Resultado delProblema 7'26- Estado actual Entrada X Estado futuro Salida Io Io I1 Il I2 I2 I3 I3 I^ I4 0 I 0 1 0 I 0 1 0 I Io I1 Il I2 I2 I3 I3 I4 I4 Io I 1 I 0 0 0 0 0 0 0 0 7.27. Obtener la tabla de estadosdel diagramade flujos de la Figura 7'8ó' AUTOMATAS FINITOS 359 X : 1 x=o tolo0 x=1 . Y l.,l01 ) , / x:0 I I T ffi { (') Figura 7.86' Enunciadodel Problema -l '27'

- 41. 360 ELEcrRoNtcA DtGtrAL Solución: Tabfa 7.53. Resultado del Problema 7.2-l Estado actual Entrada X Estado futuro Salida Io Io Il I1 I2 I2 I3 I3 0 I 0 1 0 I 0 I I1 Il I3 Il I2 Io I3 I2 0 0 0 0 I I 1 I 0 0 1 1 0 0 I I 7.28. Obtener la tabla de excitacióndel diagramade flujos de la Figura7.86 si se pretendeimplementarel circuito con biestablesdel tipo J-K. Solución: Tabla 7.54. Resultado del problemaT.2g Estado actual Qro¡ Qoot X Estado futuro Qt$+t¡ Qoo*tt Jl Kr Jo Ko ^tl .so 0 0 0 0 I I I I 0 0 I I 0 0 1 I 0 I 0 1 0 I 0 1 I 0 1 I 0 I 0 I I 1 I I I 0 0 1 0 I 0 1 0 X X X X X X X X 0 I 0 0 I 1 X X 0 0 X X X X 0 0 X X 0 I 0 0 0 0 1 1 I I 0 0 I I 0 0 I I 7.29. Obtcner la tabla de excitacióndel problema anterior si se utilizan biestables del tipo L Solución: Tabla 7.bs. Resultadodel problema 7.2g Estadoactual Qrr,, Qot,t X Estado futuro Q¡(t+t) Qoo+t) Tt To ^Sr so 0 0 0 0 I I I I 0 0 I I 0 0 I I 0 I 0 I 0 1 0 I t I 0 I 0 1 0 I I I 1 I I 0 0 I 0 1 0 I 0 0 I 0 0 1 I I 0 0 0 0 0 I 0 0 0 0 0 1 0 l l 0 l 0 1 l 1 l

- 42. 7.30. Obtener la tabla de excitacióncorrespondiente para su implementaciónun biestablegenérico Tabla 7.56. AUTOMATAS FINITOS 361 de flujos de la Figura 7.81si se emplea de verdad es la que se muestra en la al diagrama cuya tabla l''10 l,l0 Figura7.87. Diagrama de flujos. Solución: Tabla 7.56. Tabla de verdad de un biestable genérico(Problema7.30) Tabfa 7.57. Resultado del Problema7.30 x=1 Y X Qt,*rt 0 1 0 1 0 0 I ,| Q, 0 I I Q, Estadoactual Qa,t Qto¡ Qrr,, X Estado futuro Qztt+tl Qte*t) Quo*tl Y2 x2 Xr Yl xo Yo s 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 l l 0 l l 1 0 0 1 0 0 t 0 l l 0 l 0 1 0 I 0 I 0 I 0 I 0 I 0 0 0 0 0 1 0 0 1 0 1 0 r 0 1 0 l l 1 0 0 0 l l 1 0 0 t 0 l 1 0 1 0 l l x l x 1 X I x l x 0 x l x 0 x l 1 x l x l x 0 x x l x l x l x 0 0 x l x 0 x l x x l x l x 1 x 0 x 1 x 0 l x 0 x x 0 x 0 0 x l x x l x 0 l x l x 0 0 0 0 0 0 I I I 1 I I I

- 43. 362 ELECTRoN rcADrcrrAL 7.31. (t¡Itstruir la tabla de excitaciónde un contador binario de tres bits utilizandopara su realización brrestables tipo L Solución: I es la señalde control de sentidode cuenta.Con B es el ¿lcarreo de arrastredecreciente. C es el arrastrede sentidocreciente. A :0 decrementa y con A : I incrementa. Tabla 7.58. Resultado del Problema7.31 q) J A ) f (.) r r O () r I I 0 ) l q.¡ X e ? i i € l I I t Control A Estado actual Qrot Qtu¡ Qot¡ Estado futuro Qzv+tl Qr(,*r) Qq,*rt T2 Tr To Acarreo c(+) B(-) 0 0 0 0 0 0 0 0 1 I I I I I 1 1 0 0 U 0 I I I ,| 0 0 0 0 I I I 1 0 0 I I 0 0 I I 0 0 1 I 0 0 I I 0 1 0 I 0 I 0 I 0 I t 0 1 0 I 0 I I 0 0 0 0 I I I 0 0 0 I I 1 I 0 I 0 0 1 I 0 0 I 0 I I 0 0 I I 0 I 0 1 0 I 0 1 0 I 0 I 0 I 0 I 0 I 0 0 0 1 0 0 0 0 0 0 I 0 0 0 1 I 0 I 0 I 0 1 0 0 I 0 I o 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 I 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

- 44. 7.32. Construir la tabla de transicióny control nal de dos bits mediantebiestables tipo 7 Solución: R: Control de desplazamiento ED: Entrada de datos SR: Salidade datos Variables entrada AUTOMATAS FINITOS 363 de un registrode desplazamiento bidrreccro- Variables salida para el diseño síncronos. r I Y I q ) d l d 0 ) ñ ' = I Q N I I q ) l I L ( I o l (.) | t r ; I F l ? l N v t j ( ) t o " ! | u ) l L Tabfa 7.59. Resultado del Problema -1.32 Control Estados actuales Estados futuros Entradas biestables R ED Qtot Qro Qrt,*r) Qztt+t) T2 Tr SD 0 0 0 0 0 0 0 0 I 1 I 1 1 1 1 1 0 0 0 0 I I '| 1 0 0 0 0 I 1 I I 0 0 0 1 l 0 l l 0 0 0 1 1 0 l l 0 0 0 l l 0 l 1 0 0 0 1 l 0 l 1 0 0 l 0 0 0 1 0 0 1 t 1 0 1 t l 0 0 0 0 0 l 0 1 l 0 1 0 1 1 l l 0 0 1 l 1 0 0 1 0 l l 0 1 1 0 0 0 0 0 l l 1 l 0 1 0 l l 0 l 0 0 0 0 I 1 0 0 1 1 0 ,| ¡ 0 I 0 I 0 I

- 45. 364 7.33. E L E C T R O N I C A D I G I T A L Diseñar un contador de décadassíncronocon biestables -r-K. Solución: Clock F i g u r a 7.88. Resultado del Problema 7.33.