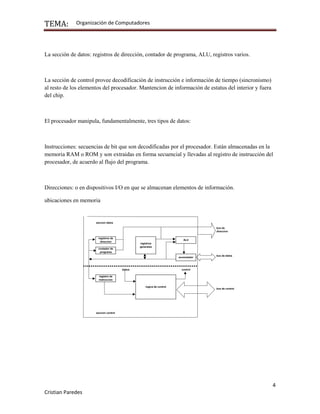

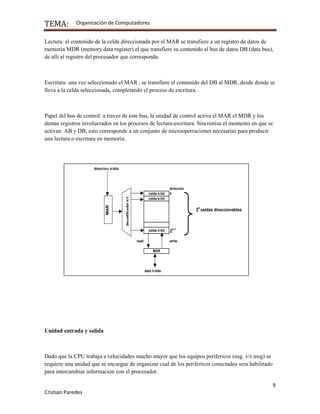

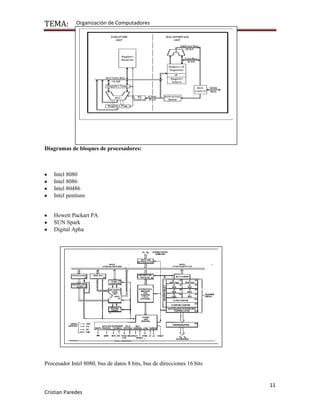

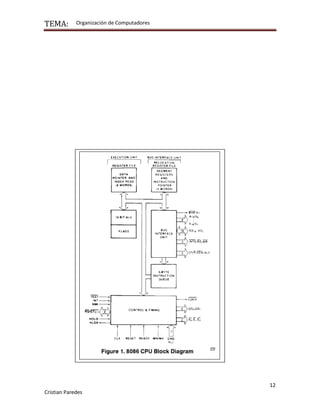

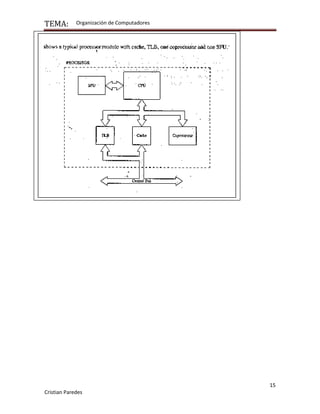

Este documento describe la arquitectura de un procesador de 32 bits típico. Consiste en las siguientes unidades funcionales: la unidad de control, la unidad aritmética lógica, los registros de trabajo, la memoria y la unidad de entrada/salida. La unidad de control sincroniza las operaciones mediante señales de reloj y decodifica las instrucciones. La unidad aritmética lógica realiza operaciones como sumas y restas. Los datos se almacenan en la memoria y se transfieren entre unidades a través de buses