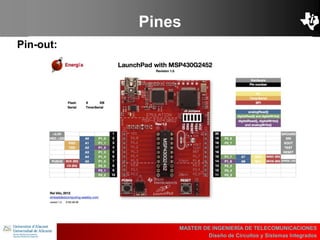

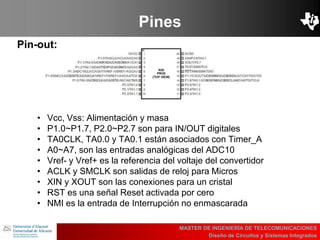

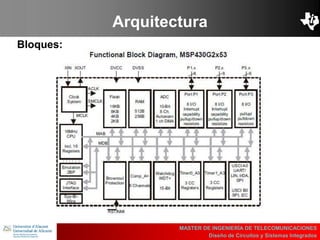

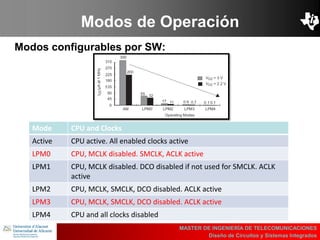

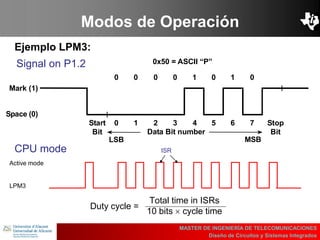

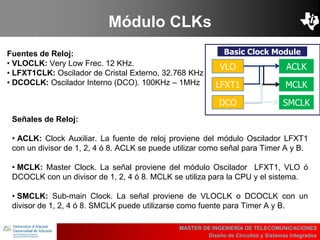

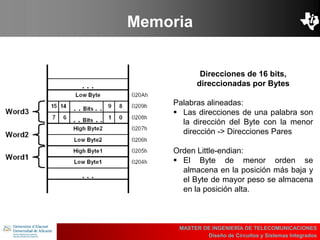

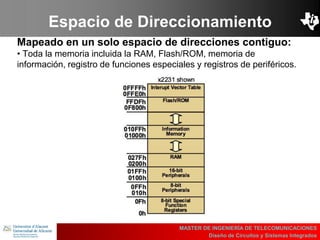

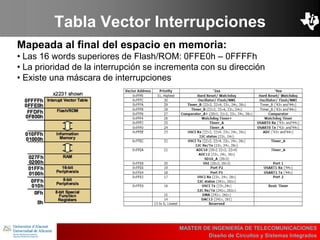

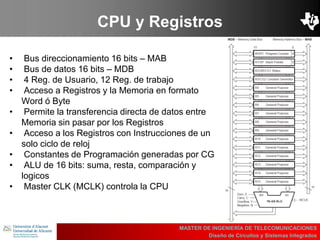

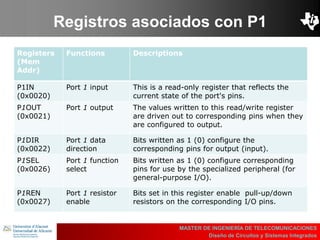

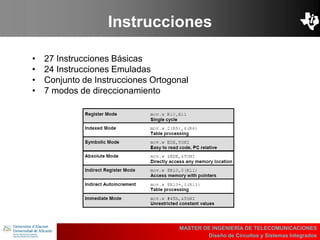

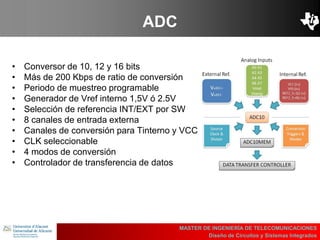

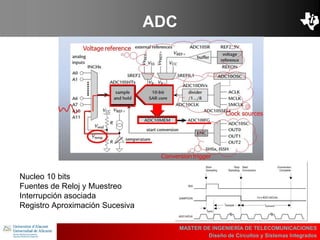

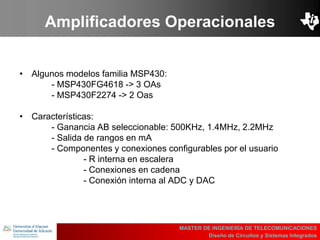

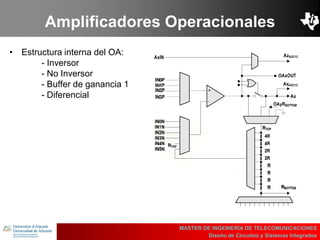

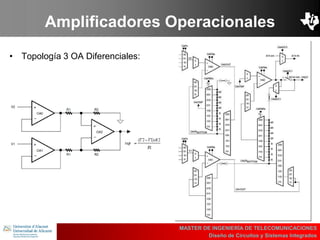

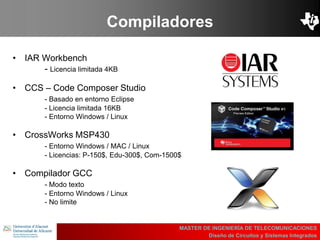

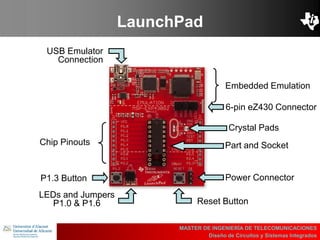

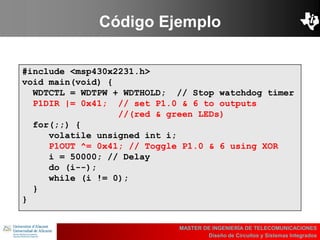

Este documento describe las características del microcontrolador MSP430, incluyendo su bajo consumo, integración, costo y arquitectura. El MSP430 tiene un CPU RISC de 16 bits, memoria flash hasta 256 KB, entradas/salidas digitales y analógicas, temporizadores, y puede operar desde 1.8V hasta 3.6V. El documento también explica el uso de periféricos como el ADC, amplificadores operacionales, y cómo programar el MSP430 usando compiladores como IAR y CCS.