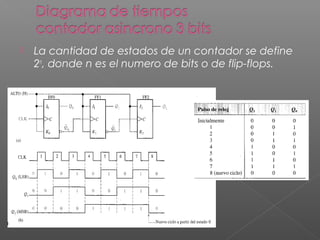

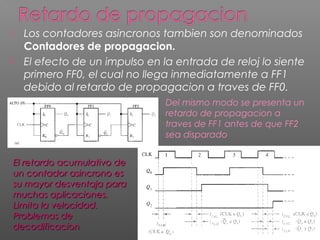

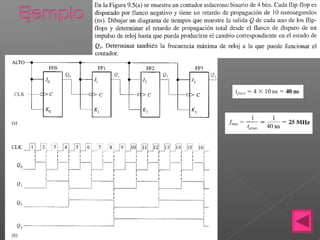

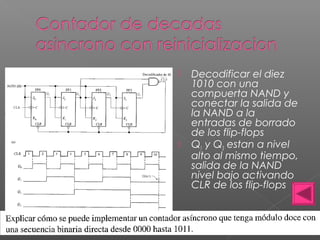

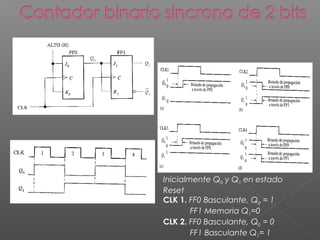

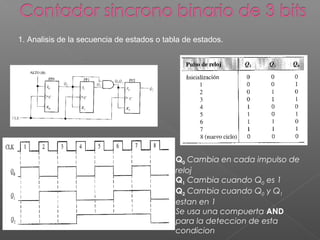

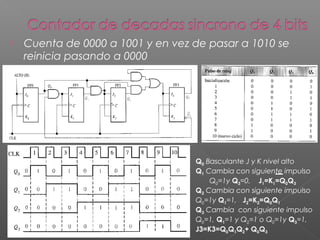

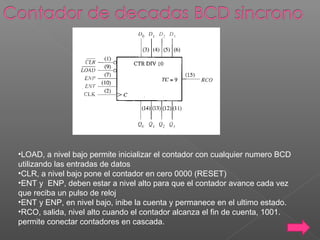

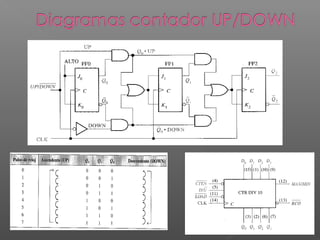

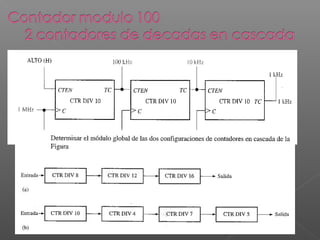

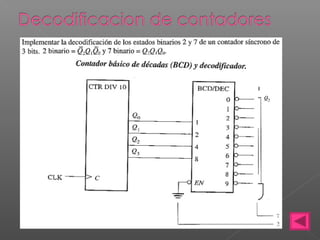

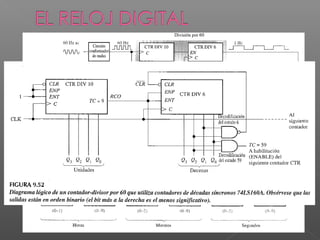

Este documento describe diferentes tipos de contadores digitales, incluyendo sus aplicaciones, clasificaciones, diseños y operación. Explica cómo los contadores se construyen utilizando flip-flops y cómo se pueden conectar en cascada para contar hasta módulos mayores. También cubre temas como contadores asincrónicos, sincrónicos, BCD y de división de frecuencia.