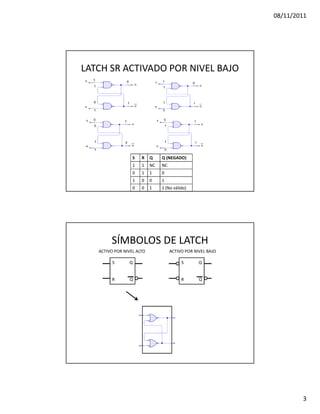

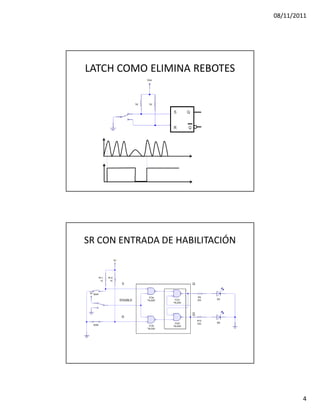

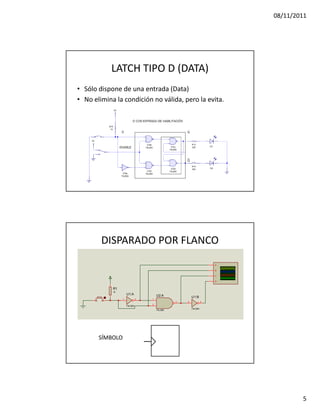

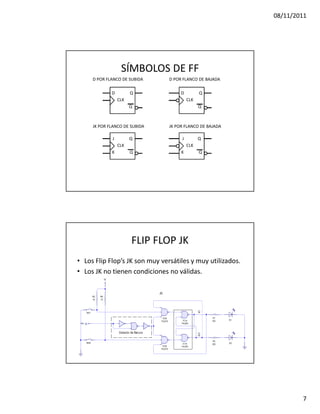

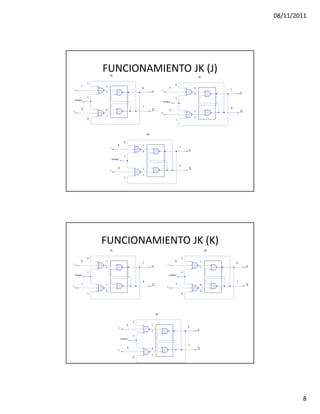

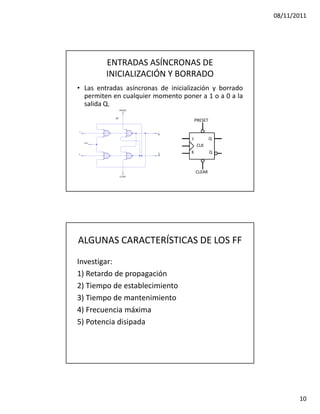

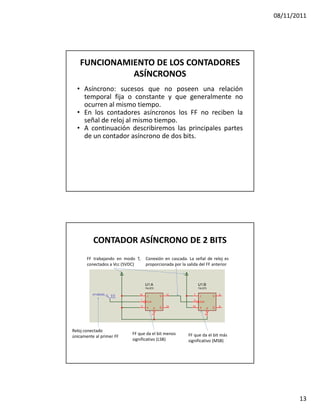

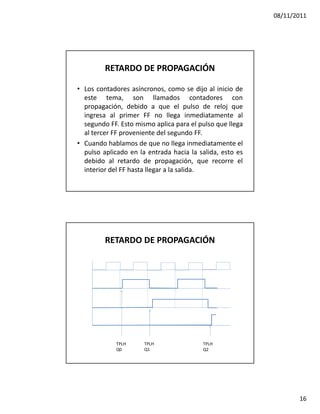

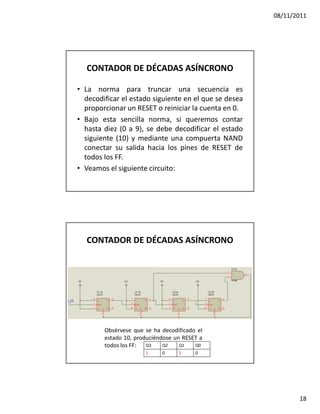

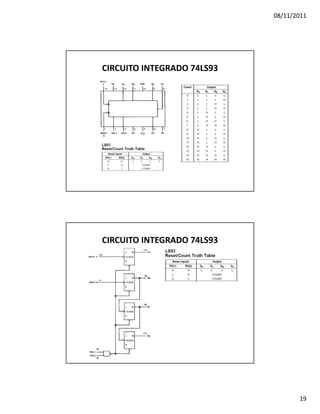

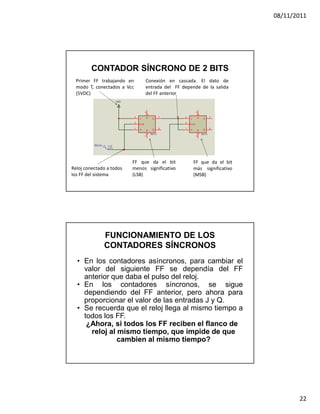

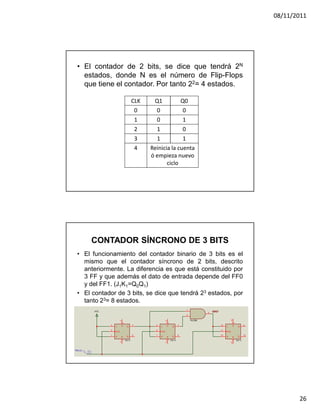

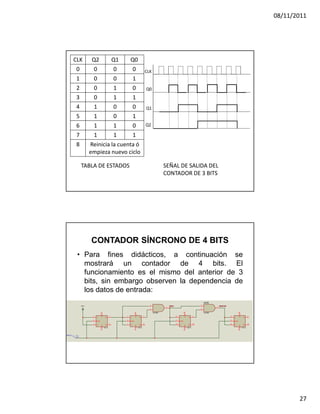

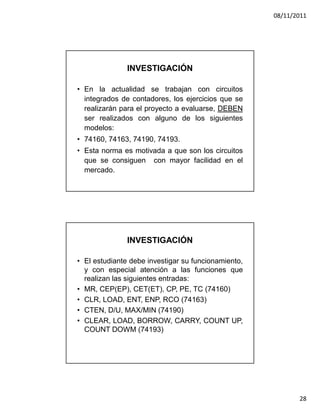

El documento introduce los sistemas secuenciales y dispositivos de almacenamiento como latchs y flip-flops. Explica el funcionamiento de latchs SR y flip-flops JK, y sus tablas de verdad. También describe contadores asíncronos de 2 y 3 bits y cómo funcionan, así como el uso de compuertas lógicas para truncar secuencias y hacer contadores de décadas. Finalmente, presenta el circuito integrado 74LS93 y una guía de ejercicios sobre diseño de contadores.