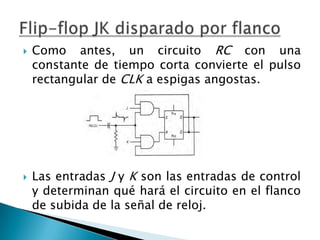

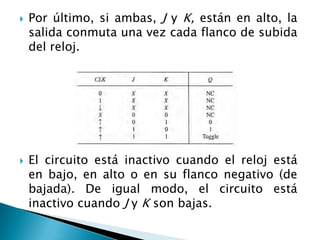

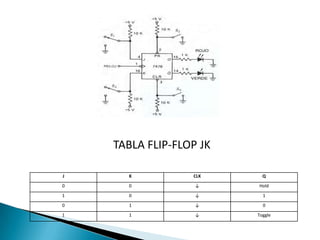

Este documento describe diferentes tipos de circuitos flip-flop digitales, incluyendo flip-flops RS, D, T y JK. Explica cómo funcionan y sus tablas de verdad. También detalla los materiales necesarios y los pasos para construir y observar flip-flops RS en el laboratorio.