El proyecto consiste en diseñar un decodificador de datos que recibe tramas de 10 bits con un formato específico y valida su secuencia. El circuito, controlado por un botón de inicio y un reloj, identifica errores en la trama y muestra resultados en un display de siete segmentos. Incluye un controlador basado en VHDL para manejar las señales internas y asegurar el correcto funcionamiento del decodificador.

![5.- DIAGRAMA DE TIEMPO

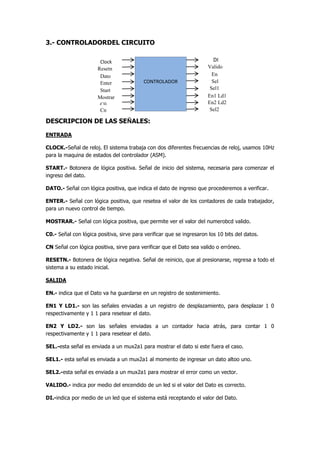

Figura 4

Del circuito controlador principal, que debe indicar todas las señales de entrada

y salida del mismo. Este diagrama debe obtenerse de la simulación previa del

sistema en MAX+PLUS II.

6.- ESQUEMATICO: Quartus II

Figura 5

Compilación del esquemático junto con todo los vhdl agregados al proyecto,

mostrándonos una respectiva ejecución con éxito.

VCC

Resetn INPUT

VCC

Dato INPUT

VCC

Enter INPUT

VCC

Start INPUT

VCC

Mostrar INPUT

VCC

Pulso INPUT

VCC

Auto INPUT

ValidoOUTPUT

EinicioOUTPUT

Ef ormatoOUTPUT

Ef inOUTPUT

DIOUTPUT

Display [1..7]OUTPUT

Resetn

Clock

Dato

Enter

Start

Mostrar

Valido

Einicio

Ef ormato

Ef in

DI

Display [1..7]

data_decoder

inst

CLOCK_8MHz CLOCK_1MHz

CLOCK_100KHz

CLOCK_10KHz

CLOCK_1KHz

CLOCK_100Hz

CLOCK_10Hz

CLOCK_1Hz

CLOCK_DIV

inst1

PB_N

CLOCK_100Hz

PB_SIN_REBOTE

ANTIREBOTE

inst3 PB_SIN_REBOTE

CLOCK

UN_PULSO

RELOJ

inst4

A

B

Sel

S

mux21

inst2](https://image.slidesharecdn.com/carpetaproyecto1-130915170131-phpapp01/85/Decodificador-de-datos-en-vhld-y-usando-Quartus-II-6-320.jpg)