Jfet prueba

- 1. TRANSISTOR DE EFECTO DE CAMPO DE UNIÓN (JFET) Ing. Alexis Barrios Ulloa MSc.

- 2. Objetivos Conocer la estructura interna y el funcionamiento del transistor de efecto de campo (JFET). Diferenciar el comportamiento de un transistor de efecto de campo de canal N con respecto a uno de canal P. Identificar las características eléctricas y de fabricación mas importantes a tener en cuenta al momento de seleccionar un transistor de efecto de campo. Hacer uso adecuado de la hoja de datos de un transistor de efecto de campo. JFET Ing. Alexis Barrios U. MSc

- 3. Transistor de efecto de campo (FET) El FET (Transistor de Efecto de Campo de Unión) es un dispositivo semiconductor de tres terminales que opera con una unión pn polarizada en inversa para controlar corriente en un canal semiconductor. (Floyd, 2008) A diferencia de los transistores BJT, los FET son dispositivos unipolares, ya que la corriente existe tanto en forma de electrones como de huecos (Savant, 2000) JFET Ing. Alexis Barrios U. MSc

- 4. Estructura de un FET JFET Ing. Alexis Barrios U. MSc Imagen tomada de: (Floyd, 2008)

- 5. Estructura de un FET Imagen tomada de: (Boylestad y Nashelsky, 2009) JFET Ing. Alexis Barrios U. MSc

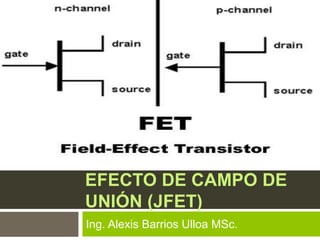

- 6. Simbología esquemática del FET JFET Ing. Alexis Barrios U. MSc

- 7. Efecto de campo La tensión de alimentación del drenador es positiva y la de la puerta negativa. El término efecto de campo se relaciona con las zonas de deplexión que rodean a cada zona p. Las uniones entre cada zona p y las zonas n tienen capas de deplexión debido a que los electrones libres se difunden desde las zonas n en las zonas p. (Malvino, 1999) Imagen tomada de: (Malvino, 1999) JFET Ing. Alexis Barrios U. MSc

- 8. Ventajas de los FET sobre los BJT De acuerdo con Floyd (2008), entre las ventajas que se tienen al usar transistores de efecto de campo sobre transistores bipolares se tienen las siguientes: Alta impedancia de entrada (de 107 a 1012 Ω). Los FET generan un nivel de ruido menor que los BJT. Los FET son, en general, mas fáciles de fabricar pues suelen requerir menos pasos de enmascaramiento y difusiones. Es posible fabricar un mayor número de dispositivos en un circuito integrado. Los FET se comportan como resistores variables controlados por tensión para valores pequeños de drenaje a fuente. La alta impedancia de entrada de los FET les permite almacenar carga el tiempo suficiente para permitir su uso como elemento de almacenamiento. Los FET de potencia pueden disipar una potencia mayor y conmutar grandes corrientes. Los FET son mas estables a la temperatura que los BJT. JFET Ing. Alexis Barrios U. MSc

- 9. Desventajas de los FET sobre los BJT De acuerdo con Floyd (2008), entre las desventajas que se pueden presentar al usar transistores de efecto de campo sobre transistores bipolares se tienen las siguientes: Los FET exhiben una respuesta en frecuencia pobre debido a su alta impedancia de entrada. Algunos tipos de FET presentan una linealidad muy pobre. Los FET son susceptibles de daño debido a la electricidad estática. JFET Ing. Alexis Barrios U. MSc

- 10. Operación básica de los FET Imagen tomada de: (Floyd, 2008) JFET Ing. Alexis Barrios U. MSc

- 11. Construcción del FET En el caso del JFET tipo n, se construye utilizando una cinta de material tipo n con dos materiales de tipo p difundidos en ella, uno a cada lado. La parte superior del canal tipo n está conectada mediante un contacto óhmico a un terminal conocido como drenaje (D), en tanto que el extremo inferior del mismo material está conectado mediante un contacto óhmico a una terminal conocida como fuente (S). Los dos materiales tipo p están conectados entre sí y a la terminal de compuerta (G). Sin potenciales aplicados, el JFET tiene dos uniones p-n en condiciones sin polarización. El resultado es una región de empobrecimiento en cada unión, la cual se asemeja a la misma región de un diodo en condiciones sin polarización (Boylestad y Nashelsky, 2009)JFET Ing. Alexis Barrios U. MSc Imagen tomada de: (Boylestad y Nashelsky, 2009)

- 12. VGS = 0 V, VDS algún valor positivo En el instante en que se aplica VDD, los electrones son atraídos hacia el drenaje y se establece la corriente convencional ID. las corrientes a través del drenaje y la fuente son equivalentes (ID = IS). la región de empobrecimiento es más ancha cerca de la parte superior de ambos materiales tipo p. El hecho de que la unión p-n se polarice en inversa a lo largo del canal produce una corriente de cero amperes en la compuerta (Boylestad y Nashelsky, 2009). Imagen tomada de: (Boylestad y Nashelsky, 2009) JFET Ing. Alexis Barrios U. MSc

- 13. Tensión de estrangulamiento Conforme el voltaje VDS aumente de 0 V a algunos volts, la corriente también lo hará de acuerdo con la ley de Ohm. La pendiente constante relativa de la gráfica revela que en la región de valores bajos de VDS, la resistencia en esencia es constante. A medida que VDS se incrementa y se aproxima un nivel conocido como Vp, las regiones de empobrecimiento se ensanchan, lo que reduce notablemente el ancho del canal. La ruta reducida de conducción hace que la resistencia se incremente, y ocurra la curva en la gráfica de la figura (Floyd, 2008)JFET Ing. Alexis Barrios U. MSc Imagen tomada de: (Boylestad y Nashelsky, 2009)

- 14. Corriente de drenaje (IDSS) Un incremento continuo de VDS por encima del voltaje de estrangulamiento produce una corriente casi constante en el drenaje. Este valor de la corriente en el drenaje es IDSS (Drain to Source with gate Shorted, Drenaje a fuente con la compuerta en cortocircuito) y siempre viene especificada en las hojas de datos de los JFET. IDSS es la corriente máxima en el drenaje que un JFET específico es capaz de producir sin importar el circuito externo y siempre se especifica en la condición, VGS = 0 V y VDS > |Vp| (Floyd, 2008).JFET Ing. Alexis Barrios U. MSc Imagen tomada de: (Boylestad y Nashelsky, 2009)

- 15. Región óhmica la tensi6n de estrangulamiento separa las dos zonas principales de funcionamiento del JFET. La parte casi horizontal es la zona activa. La parte casi vertical de la curva de salida se llama zona óhmica. Cuando un JFET funciona en la zona 6hmica actúa como una resistencia pequeña con un valor aproximado de: 𝑅 𝐷𝑆 = 𝑉𝑝 𝐼 𝐷𝑆𝑆 Si el JFET funciona en cualquier lugar de la zona óhmica, tiene una resistencia de 400Ω. (Floyd, 2008). Imagen tomada de: (Floyd, 2008) JFET Ing. Alexis Barrios U. MSc

- 16. Ruptura la ruptura ocurre en el punto C cuando ID comienza a incrementarse muy rápido con cualquier incremento adicional de VDS. La ruptura puede dañar irreversiblemente el dispositivo, así que los JFET siempre se operan por debajo de la ruptura y dentro de la región activa, (corriente constante) (Floyd, 2008). Imagen tomada de: (Floyd, 2008) JFET Ing. Alexis Barrios U. MSc

- 17. VGS < 0V JFET Ing. Alexis Barrios U. MSc Imagen tomada de: (Floyd, 2008)

- 18. Voltaje de corte El valor de VGS que hace que ID sea aproximadamente cero es el voltaje de corte. El JFET debe operar entre VGS 0 V y VGS(corte). Con este intervalo de voltajes de compuerta a fuente, ID varía desde un máximo de IDSS hasta un mínimo de casi cero. Mientras más negativo es VGS, más pequeña llega a ser ID en la región activa. Cuando VGS tiene un valor negativo suficientemente grande, ID se reduce a cero. El estrechamiento de la región de empobrecimiento provoca este efecto de corte hasta un punto donde el canal se cierra por completo. (Boylestad y Nashelsky, 2009). Imagen tomada de: (Floyd, 2008) JFET Ing. Alexis Barrios U. MSc

- 19. Características de transferencia La característica de transferencia es una gráfica de la corriente de drenaje ID, como función de la tensión compuerta a fuente , VGS, por encima del estrangulamiento. Se grafica con VDS igual a una constante, aunque la característica de transferencia es en esencia independiente de VDS pues, luego de que el FET llega al estrangulamiento, Id permanece constante para valores mayores de VDS JFET Ing. Alexis Barrios U. MSc Imagen tomada de: (Floyd, 2008)

- 20. Características de transferencia Imagen tomada de: (Boylestad y Nashelsky, 2009) JFET Ing. Alexis Barrios U. MSc

- 21. Ecuación de Shockley En los JFET no existe una relación lineal entre las cantidades de entrada y salida. La relación entre ID y VGS está definida por la ecuación de Schockley: 𝐼 𝐷 = 𝐼 𝐷𝑆𝑆 1 − 𝑉𝐺𝑆 𝑉𝑃 2 El termino al cuadrado en la ecuación produce una relación no lineal entre ID y VGS lo cual produce una curva que crece exponencialmente con la magnitud decreciente de VGS (Savant, 2000). Variable de control Constante s JFET Ing. Alexis Barrios U. MSc

- 22. Método abreviado la curva de transferencia se puede trazar con un nivel de precisión satisfactorio con sólo utilizar los cuatro puntos definidos anteriormente y revisados en la tabla 1: Tabla 1 VGS contra ID VGS ID 0 V IDSS 0.3 Vp IDSS/2 0.5 Vp IDSS/4 Vp 0 mA JFET Ing. Alexis Barrios U. MSc

- 23. Referencias Electrónica II Ing. Alexis Barrios Floyd, T. (2008). Dispositivos Electrónicos. Octava edición. Ciudad de México, México: Editorial Pearson. Savant, C. J. (2000). Diseño Electrónico: Circuitos y Sistemas. Tercera edición. Ciudad de México, México: Editorial Alhambra. Boylestad, R. Nashelsky, L. (2009). Electrónica: Teoría de Circuitos y Dispositivos electrónicos. Décima edición. Ciudad de México, México: Editorial Pearson. [2] Malvino, A., Principios de Electrónica. Sexta edición. Editorial Mc Graw Hill. Madrid. 1999.

Notas del editor

- Al comparar el FET con el BJT, se aprecia que el drenaje es análogo al colector, en tanto que la fuente es análogo al emisor, mientras que la compuerta es análoga a la base. La fuente y el drenaje de un FET se pueden intercambiar sin afectar la operación del transistor.

- Si VDS se incrementa a un nivel donde pareciera que las dos regiones de empobrecimiento “se tocarán”; se originará una condición conocida como estrangulamiento El nivel de VDS que establece esta condición se conoce como voltaje de estrangulamiento y lo denota Vp,

- Si VDS se incrementa a un nivel donde pareciera que las dos regiones de empobrecimiento “se tocarán”; se originará una condición conocida como estrangulamiento El nivel de VDS que establece esta condición se conoce como voltaje de estrangulamiento y lo denota Vp,

- Debido al termino al cuadrado, los JFET también son conocidos como dispositivos de ley cuadrática.

- Debido al termino al cuadrado, los JFET también son conocidos como dispositivos de ley cuadrática.

- Debido al termino al cuadrado, los JFET también son conocidos como dispositivos de ley cuadrática.