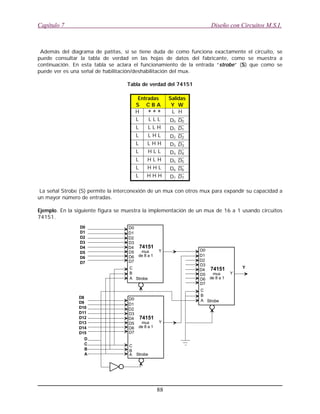

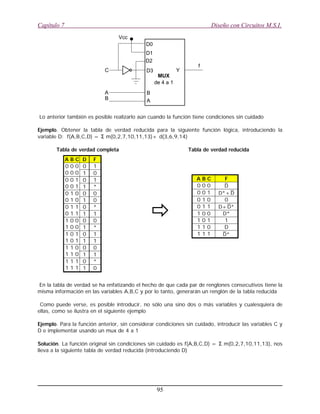

Este documento describe los circuitos integrados de media escala de integración (MSI) y su uso en el diseño de circuitos lógicos. Explica que los circuitos MSI representan soluciones ya hechas a problemas comunes de lógica combinacional y secuencial. Luego describe varios tipos de circuitos MSI como sumadores, multiplexores y decodificadores, e ilustra su funcionamiento y aplicaciones mediante ejemplos como sumadores BCD y convertidores numéricos. Finalmente, destaca las ventajas del uso de circuitos MSI como soluciones compactas,