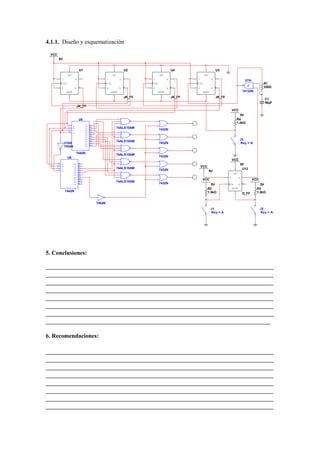

Este documento describe el diseño de un sistema secuencial automático que controla 5 LEDs usando flip-flops. El sistema cuenta con pulsadores para iniciar, detener y reiniciar la secuencia de los LEDs. El procedimiento incluye el diseño del circuito usando flip-flops JK, compuertas lógicas y una tabla de verdad para especificar los estados y salidas.