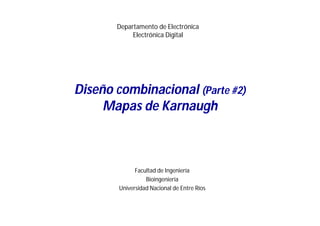

Este documento presenta el método de mapas de Karnaugh para simplificar funciones lógicas. Explica cómo construir mapas de Karnaugh para funciones de diferentes números de variables y cómo agrupar celdas adyacentes con el mismo valor para eliminar variables y simplificar la función. También cubre el uso de celdas con valores "no importa" y proporciona ejemplos del proceso de simplificación mediante mapas de Karnaugh.

![Ejemplo: detector de números BCD pares

DC

00 01

00

01

BA

0 4

1 5

12 8

13 9

11 10

3 7

2 6

15 11

14 10

11

10 1

1

1

1 1

Z = D/A/ + A/B/C/

Z = [(D+A)/ + (A+B+C)/]// (todo NOR)

#compuertas: 7

#CIs: 3 (1 INV, 1 AND 3i, 1 OR 2i)

#compuertas: 4

#CI: 2 (1 NOR 2i, 1NOR 3i)](https://image.slidesharecdn.com/karnaugh-230307093003-f4330856/85/karnaugh-pdf-20-320.jpg)