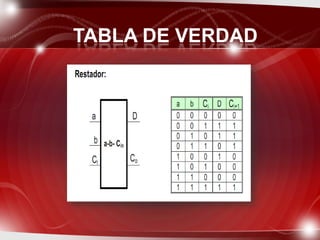

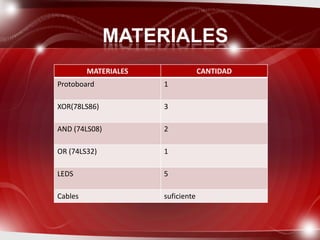

Este documento describe un sumador-restador de 4 bits. Explica que un sumador es un circuito lógico que realiza la operación de suma, mientras que un restador realiza la operación de resta. Cuando se usa complemento a dos para representar números negativos, un sumador puede convertirse en un sumador-restador capaz de realizar ambas operaciones. Luego, detalla los componentes de hardware necesarios para implementar un sumador-restador de 4 bits, incluidas compuertas lógicas como XOR, AND y OR, así como LEDs y cables.