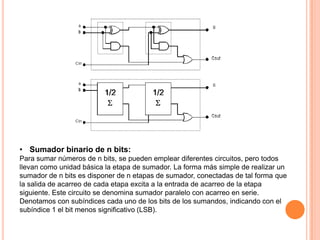

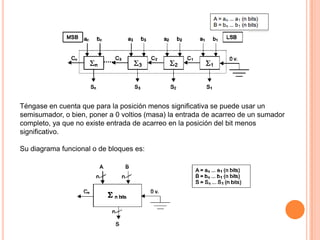

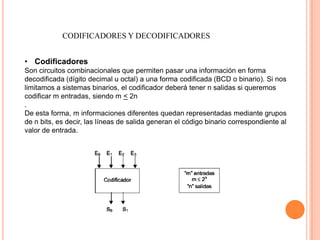

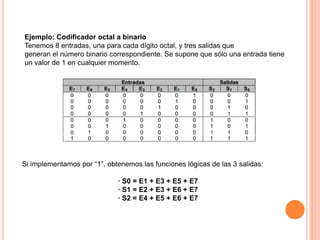

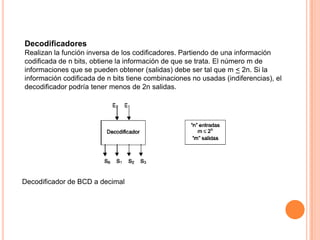

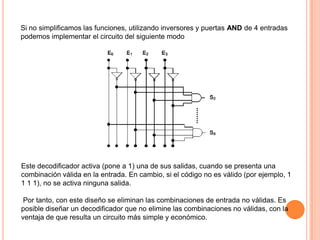

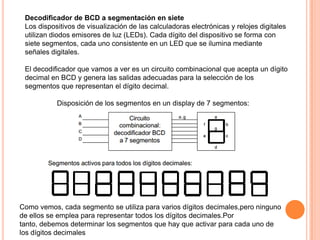

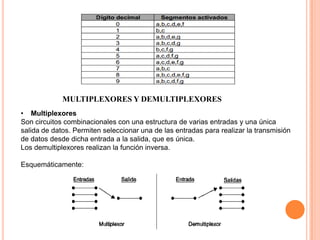

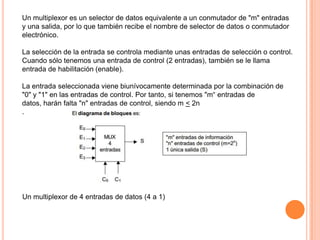

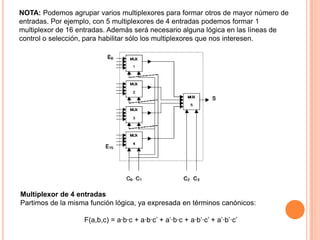

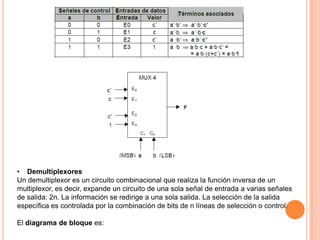

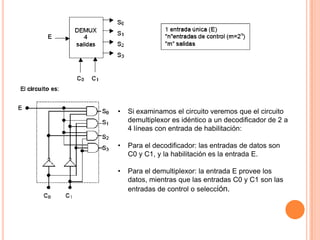

Este documento describe los circuitos combinacionales, los cuales tienen varias entradas y salidas donde la relación entre cada salida y las entradas puede expresarse mediante una función lógica. Explica que cada salida depende exclusivamente de las entradas en el mismo instante de tiempo, sin depender de entradas anteriores. Además, describe sumadores, codificadores, decodificadores, multiplexores y demultiplexores como ejemplos de circuitos combinacionales.