Este documento analiza y compara máquinas de estado de Mealy y Moore. Explica cómo implementar un sumador serial como máquina de Mealy y Moore, obteniendo ecuaciones de estado, tablas de estados y diagramas de estados. También discute diferencias clave como que en una máquina de Mealy las salidas dependen del estado actual y las entradas, mientras que en una máquina de Moore la salida depende solo del estado actual.

![PROCEDIMIENTO:

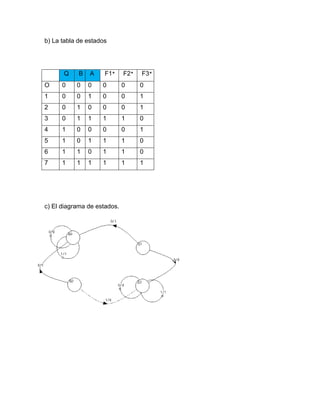

DESARROLLO

Máquinas de Mealy

1. Analice en forma teórica el siguiente circuito, el cual corresponde a un sumador serial.

Observe que la salida suma depende de las entradas A, B y el estado interno C.

Figura 4.1: Circuito sumador serial implementado como máquina de Mealy.

Obtenga:

a) Las ecuaciones para D, Ct+1 y suma.

D = Q*B + [ (Q B) *A ]

Ct+1 = Q*B + [ (Q B) *A ]

Suma = (Q B) *~A + [ (~ (Q B)) * A ]](https://image.slidesharecdn.com/taller4josuestanleylazorivera-141203180222-conversion-gate02/85/Taller-4-josue-stanley-lazo-rivera-3-320.jpg)