Electrónica digital: Análisis de síntesis de circuitos secuenciales

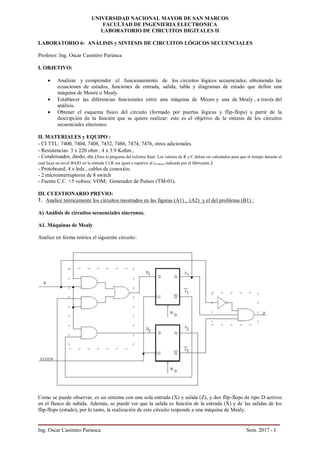

- 1. Ing. Oscar Casimiro Pariasca Sem. 2017 - I UNIVERSIDAD NACIONAL MAYOR DE SAN MARCOS FACULTAD DE INGENIERIA ELECTRONICA LABORATORIO DE CIRCUITOS DIGITALES II LABORATORIO 6: ANÁLISIS y SINTESIS DE CIRCUITOS LÓGICOS SECUENCIALES Profesor: Ing. Oscar Casimiro Pariasca I. OBJETIVO: Analizar y comprender el funcionamiento de los circuitos lógicos secuenciales; obteniendo las ecuaciones de estados, funciones de entrada, salida, tabla y diagramas de estado que define una máquina de Moore o Mealy. Establecer las diferencias funcionales entre una máquina de Moore y una de Mealy , a través del análisis. Obtener el esquema físico del circuito (formado por puertas lógicas y flip-flops) a partir de la descripción de la función que se quiere realizar: este es el objetivo de la síntesis de los circuitos secuenciales síncronos. II. MATERIALES y EQUIPO : - CI TTL: 7400, 7404, 7408, 7432, 7486, 7474, 7476, otros adicionales. - Resistencias: 3 x 220 ohm , 4 x 3.9 Kohm , - Condensador, diodo, etc.(Para la pregunta del informe final: Los valores de R y C deben ser calculados para que el tiempo durante el cual haya un nivel BAJO en la entrada CLR sea igual o superior al tCLRmín indicado por el fabricante.) - Protoboard, 4 x leds , cables de conexión. - 2 microinterruptores de 8 switch - Fuente C.C. +5 voltios; VOM; Generador de Pulsos (TM-01). III. CUESTIONARIO PREVIO: 1. Analice teóricamente los circuitos mostrados en las figuras (A1) , (A2) y el del problema (B1) : A) Análisis de circuitos secuenciales síncronos. A1. Máquinas de Mealy Analice en forma teórica el siguiente circuito: Como se puede observar, es un sistema con una sola entrada (X) y salida (Z), y dos flip-flops de tipo D activos en el flanco de subida. Además, se puede ver que la salida es función de la entrada (X) y de las salidas de los flip-flops (estado), por lo tanto, la realización de este circuito responde a una máquina de Mealy.

- 2. Ing. Oscar Casimiro Pariasca Sem. 2017 - I Obtener: a) Las ecuaciones lógicas de las entradas de los flip-flops b) Las ecuaciones lógicas del próximo estado: las próximas salidas de los flip-flops Q(t+1) c) La función lógica de salida del sistema. c) La tabla de transiciones o de estados codificada. d) Representar el diagrama de estados o grafo de comportamiento del sistema a partir de la tabla de estados. A2. Máquinas de Moore. Analice en forma teórica el circuito de la figura. Como se puede observar, es un circuito de una sola entrada (x), tres flip-flops de tipo D y una salida que depende únicamente de las salidas de los flip flops, por tanto, se trata de un autómata de Moore. Obtener: a) Las ecuaciones lógicas de las entradas de los flip-flops b) Las ecuaciones lógicas del próximo estado: las próximas salidas de los flip-flops Q(t+1) c) La función lógica de salida del sistema. c) La tabla de transiciones o de estados codificada. d) Representar el diagrama de estados o grafo de comportamiento del sistema a partir de la tabla de estados. B) Síntesis de circuitos secuenciales síncronos. Los pasos a seguir son prácticamente los mismos que los del proceso de análisis, pero en sentido inverso. De forma resumida estos pasos son: - Planteamiento del problema. - Obtención del diagrama de estados. - Obtención de la tabla de estados o transiciones inicial. - Minimización de la tabla de estados. - Asignación de estados y obtención de la tabla de estados o transiciones codificada. - Obtención de las ecuaciones de salida del sistema. - Obtención de las tablas de excitación y ecuaciones de entrada de cada flip-flop del circuito. - Implementación del circuito. - Inclusión de los circuitos de control de las entradas asíncronas para asegurar que, al alimentar el circuito, éste se sitúe en el estado inicial del diagrama de estados. B1. Diseño de un autómata de Mealy. “Se quiere diseñar un circuito secuencial síncrono que proporcione a su salida un nivel alto cada vez que en su línea de entrada se presente la secuencia 101". Utilize flip flop tipo JK 2. Simulación de los circuitos secuenciales síncronos. Compruebe los resultados de los análisis anteriores por medio de un simulador (Proteus) u otro.

- 3. Ing. Oscar Casimiro Pariasca Sem. 2017 - I IV. PARTE EXPERIMENTAL: 1. Verificar experimentalmente y según los resultados del análisis previo, los circuitos mostrados en las figuras (A1) , (A2). 2. En los diagramas de estado mostrados, indique cual de ellos corresponde a un autómata de Mealy o de Moore. Explique por qué. Implementar los circuitos correspondientes. 3. Compruebe los resultados de los análisis anteriores por medio del Software Isis, “Proteus” u otro simulador. V. CUESTIONARIO FINAL: 1. ¿Cuándo es preferible utilizar máquinas de Mealy? 2. ¿Cuándo es preferible utilizar máquinas de Moore? 3. ¿Cuál es la finalidad del pulsador P en el circuito mostrado?. ¿Cómo funciona este circuito?. Presentar la tabla y el diagrama de estados del circuito. 4. ¿Qué influencia tiene sobre el análisis el flanco para la transición de los Flip Flop mostrados en los circuitos? 5. ¿Cuándo se dice, en una máquina FSM, que dos estados son equivalentes? . 6. ¿Por qué no existe algún integrado comercial con Flip Flop’s tipo T? 7. Simular y dibujar las salidas Q2, Q1 y Q0 del circuito mostrado. Asuma que los tiempos de subida y bajada son igual a cero, que el retardo de propagación de los flip flop son de 1 nseg y que cada división de tiempo del gráfico mostrado es de 500 nseg (clock de 1 MHz). Asuma que las salidas empiezan con ‘0’ inicialmente. Escribir las ecuaciones de excitación, ecuaciones de transición, tabla de transición, etc. Las salidas de los circuitos son Q2Q1Q0 . Dibujar el diagrama de estados.