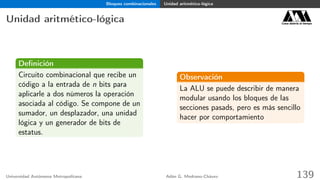

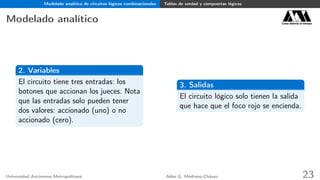

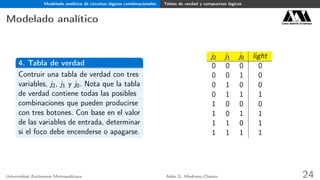

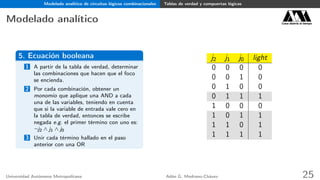

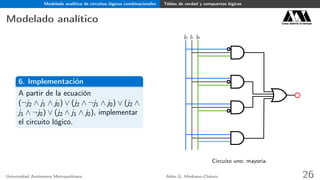

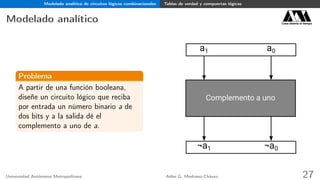

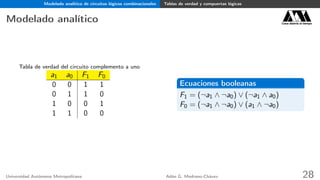

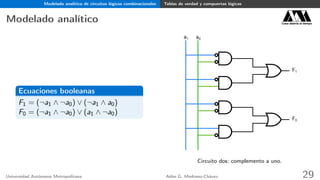

Este documento presenta una introducción a los circuitos combinacionales. Se divide en cuatro secciones principales: 1) introducción, 2) modelado analítico de circuitos lógicos combinacionales, 3) simulación de circuitos lógicos combinacionales y 4) bloques combinacionales. La segunda sección explica cómo modelar analíticamente un circuito lógico mediante tablas de verdad, funciones booleanas y su implementación con compuertas lógicas. Se incluyen ejemplos como un circuito mayoría y complemento a uno.

![Modelado analítico de circuitos lógicos combinacionales Representaciones canónicas de las funciones booleanas

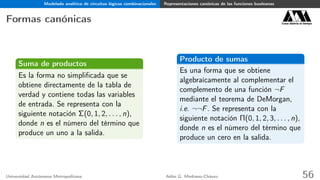

Formas canónicas Casa abierta al tiempo

Expresión Explicación

F(x, y, z) = Σ(1, 2, 3, 4, 5, 6) expresión inicial

¬F(x, y, z) = Σ(0, 7) Forma condensada del complemento de F

¬F(x, y, z) = (¬x ∧ ¬y ∧ ¬z) ∨ (x ∧ y ∧ z) Forma expandida del complemento de F

¬¬F(x, y, z) = ¬[(¬x ∧ ¬y ∧ ¬z) ∨ (x ∧ y ∧ z)] Complemento del complemento de la función

¬¬F(x, y, z) = ¬(a ∨ b) Cambio de variable

¬¬F(x, y, z) = ¬a ∧ ¬b Teorema de DeMorgan

¬¬F(x, y, z) = ¬(¬x ∧ ¬y ∧ ¬z) ∧ ¬(x ∧ y ∧ z) Regreso del cambio de variable

F(x, y, z) = (x ∨ y ∨ z) ∧ (¬x ∨ ¬y ∨ ¬z) Doble negación y teorema de DeMorgan

F(x, y, z) = Π(0, 7) Forma condensada del producto de sumas de F

Obtención del producto de sumas de la función F = Σ(1, 2, 3, 4, 5, 6)

Universidad Autónoma Metropolitana Adán G. Medrano-Chávez 58](https://image.slidesharecdn.com/combinational-170730061306/85/Combinational-logic-58-320.jpg)

![Simulación de circuitos lógicos combinacionales Contexto

Lenguaje de descripción de hardware Casa abierta al tiempo

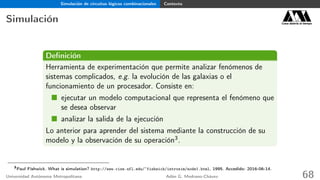

Definición4

Lenguaje de alto nivel empleado para

representar un sistema digital, e.g. un

conmutador de red (switch), un

circuito integrado de aplicación

específica (ASIC, aplication specific

integrated circuit), una memoria, un

bloque combinacional o un biestable

(flip-flop)

Ejemplos de HDL

• VDHL

• Verilog

• SystemVerilog

• Handel-C

• MyHDL

• SystemC

4

Tala, D. K., «Verilog tutorial», [en línea] http://www.asic-world.com

Universidad Autónoma Metropolitana Adán G. Medrano-Chávez 71](https://image.slidesharecdn.com/combinational-170730061306/85/Combinational-logic-71-320.jpg)

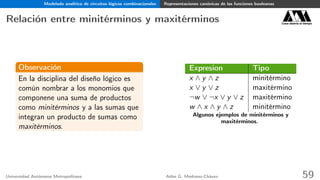

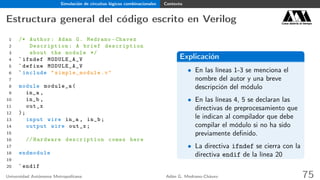

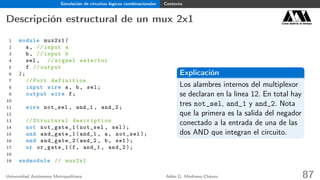

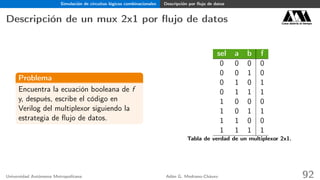

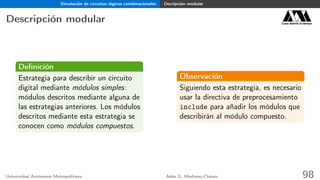

![Simulación de circuitos lógicos combinacionales Decripción modular

Descripción modular de un mux 4x1 Casa abierta al tiempo

a

b

c

d

y

sel0

sel1

0

1

0

1

0

1

mux0

mux2

mux1

o0

o1

1 `include " mux2x1_structural .v"

2

3 module mux4x1(a, b, c, d, sel , f);

4 // Port definition

5 input wire a, b, c, d;

6 input wire [1:0] sel;

7 output reg f;

8

9 // Internal wires

10 wire m_0 , m_1;

11

12 // Modular description

13 mux2x1 mux2x1_0(a, b, sel[0], mux_0 );

14 mux2x1 mux2x1_1(c, d, sel[0], mux_1 );

15 mux2x1 mux2x1_2(m_0 , m_1 , sel[1], f);

16

17 endmodule // mux4x1

Universidad Autónoma Metropolitana Adán G. Medrano-Chávez 99](https://image.slidesharecdn.com/combinational-170730061306/85/Combinational-logic-99-320.jpg)