Practicas electronica digital 1.tese.ag

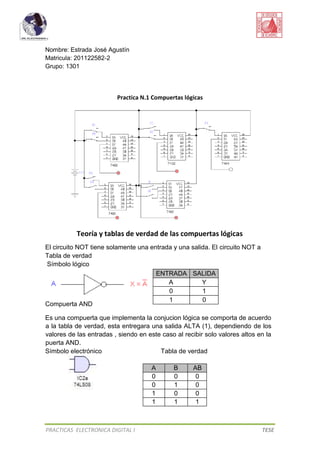

- 1. PRACTICAS ELECTRONICA DIGITAL I TESE Nombre: Estrada José Agustín Matricula: 201122582-2 Grupo: 1301 Practica N.1 Compuertas lógicas Teoría y tablas de verdad de las compuertas lógicas El circuito NOT tiene solamente una entrada y una salida. El circuito NOT a Tabla de verdad Símbolo lógico Compuerta AND Es una compuerta que implementa la conjucion lógica se comporta de acuerdo a la tabla de verdad, esta entregara una salida ALTA (1), dependiendo de los valores de las entradas , siendo en este caso al recibir solo valores altos en la puerta AND. Símbolo electrónico Tabla de verdad A B AB 0 0 0 0 1 0 1 0 0 1 1 1 ENTRADA SALIDA A Y 0 1 1 0

- 2. PRACTICAS ELECTRONICA DIGITAL I TESE Compuerta OR Se utiliza para conectar dos o mas variables y basta con que una de las señales se cumpla para que toda la función sea verdadera. Símbolo electrónico Tabla de verdad A B AB 0 0 0 0 1 1 1 0 1 1 1 1 La compuerta AND Es una puerta lógica digital que implementa la conjunción lógica -se comporta de acuerdo a la tabla de verdad Ésta entregará una salida ALTA (1), dependiendo de los valores de las entradas, siendo este caso, al recibir solo valores altos en la puerta AND. Si alguna de estas entradas no son ALTAS, entonces se mostrará un valor de salida BAJA. En otro sentido, la función de la compuerta AND efectivamente encuentra el mínimo entre dos dígitos binarios, así como la función OR encuentra al máximo. Símbolo electrónico Tabla de verdad A B AB 0 0 0 0 1 0 1 0 0 1 1 1 La compuerta NOR ES lo inverso a la compuerta OR, nadamas que cuenta con un pequeño circulo de lado derecho a su salida. Símbolo electrónico Tabla de verdad A B AB 0 0 1 0 1 0 1 0 0 1 1 0

- 3. PRACTICAS ELECTRONICA DIGITAL I TESE Practica N2. Algebra de Boole Dado el circuito, obtenga la ecuación booleana de su comportamiento, obtenga sus resultados parciales. Circuito 1 .C=A+B TABLA DE VERDAD A B AB AB+B 0 0 0 0 0 1 0 1 1 0 0 0 1 1 1 1 En la figura de arriba se muestra la tabla de verdad que corresponde de igual manera a los circuitos 1 y 3. Circuito 3.

- 4. PRACTICAS ELECTRONICA DIGITAL I TESE Obtenga la ecuación booleana y su circuito lógico correspondiente Circuito 2 .S= (A/+AB)+C Circuito 4. Tabla de verdad que corresponde al los circuitos 2 y 4 A B C A/ AB A/+AB C=(A/+AB+C) 0 0 0 1 0 1 1 0 0 1 1 0 1 1 0 1 0 1 0 1 1 0 1 1 1 0 1 1 1 0 0 0 0 0 0 1 0 1 0 0 0 1 1 1 0 0 1 1 1 1 1 1 0 1 1 1

- 5. PRACTICAS ELECTRONICA DIGITAL I TESE Practica N.3 Teorema de Boole y forma canoníca a) [AB(C+B/D/)+A/B/]CD Entonces =[ABC+ABB/D/+A/B/]CD =ABCCD+ABB/D/CD+A/B/CD =ABCD+ABB/D/CD+A/B/CD =ABCD+(B/+D/)(ABCD)+(A/+B/)(CD) =ABCD+ABBCD+ABCDD/+A/CD+B/CD =ABCD+AB(0)+AB(0)+A/CD+B/CD =ABCD+A/CD+B/CD =CD(AB+A/+B/) =CD(AB+A/B/) =CD(1) =CD CIRCUITO 1 CD TABLA DE VERDAD Circuito 2 [AB(C+B/D/)+A/B/] CD C D S 0 0 0 0 1 0 1 0 0 1 1 1

- 6. PRACTICAS ELECTRONICA DIGITAL I TESE Tabla de verdad [AB(C+B/D/)+A/B/]CD A B C D S 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 1 1

- 7. PRACTICAS ELECTRONICA DIGITAL I TESE Tabla de verdad =CD S=(A/B/CD+A/BCD+AB/CD+ABCD) B) X/Y/Z+XZ ENTONSES: =(X/Y/Z/)(X/Z/) =(XY+Z/)(X/+Z/) =(XY+Z/)(X/+Z/) =X/X//Y+XYZ/+X/Z/+X/Z/+Z/Z/ =XYZ/+X/Z/+Z/Z/ =XYZ/+X/Z/+Z/ =(XY)Z/+X/Z/+Z/ =Z/(XY+X/+1)->Factor común =Z/[(XY+X/+1)] ---> X+1=1 = Z Circuito electrónico C D S 0 0 0 0 1 0 1 0 0 1 1 1 A B C S

- 8. PRACTICAS ELECTRONICA DIGITAL I TESE ->A/ B/ C/ ->A/ B/ C ->A B/C/ Practica N.4 SIMPLIFICACIÓN POR MAPA DE KARNAUGH 0 0 0 1 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1

- 9. PRACTICAS ELECTRONICA DIGITAL I TESE Circuito Practica N.5 Circuito sumador y semi –sumador Circuito semi sumador o medio sumador Entonces: S0=B/0A0+B0A/0 =A0+B0 C0=A0B0 Tabla de verdad semi sumador ENTRADAS SALIDAS A0 B0 SO CO 0 0 0 0 0 1 1 0 0 1 1 0 1 1 0 1

- 10. PRACTICAS ELECTRONICA DIGITAL I TESE Circuito semi sumador completo Entonces:

- 11. PRACTICAS ELECTRONICA DIGITAL I TESE Circuito Sumador completo Tabla de verdad sumador completo Ci Bo Ao So Co 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 Practica N.6 Circuito restador Circuito restador Un restador completo es un circuito combinacional que lleva a cabo una sustracción entre dos bits, tomando en cuenta en un 1 se ha tomado por una etapa significativa más baja. ¿CÓMO ESTA CONFORMADO?

- 12. PRACTICAS ELECTRONICA DIGITAL I TESE Este circuito tiene tres entrada y dos salidas. Las tres entradas A, B , CIN, denotan al minuendo, sustraendo y a la toma previa, respectivamente. Las dos salidas, S y COUT, representan la diferencia y la salida tomada, respectivamente. Tabla de verdad A B Ci S C Signo 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 1 0 1 1 0 0 0 1 0 0 1 0 0 1 0 1 0 1 0 1 1 0 0 0 0 1 1 1 1 0 0 Practica N.7 Circuito Multiplicador de 2 bits

- 13. PRACTICAS ELECTRONICA DIGITAL I TESE Practica N.8 Flip flops Son circuitos lógicos diseñados para guardar un bit de un número binario. Las salidas de un flip flops son Q y Q/ y deben tener siempre estados lógicos diferentes. Los Flip – Flops son dispositivos síncronos, de dos estados, también conocidos como multivibradores biestables. Un Flip - Flop se diferencia de un Latch, en la forma en que cambian sus datos de salida, ya que es un dispositivo controlado por una señal de reloj, en el cual solamente cambiará sus datos de salida mientras ocurra un flanco de subida o de bajada de una señal de reloj, como lo indica la entrada dinámica.

- 14. PRACTICAS ELECTRONICA DIGITAL I TESE Flip flop JK (a) Positive edge-triggered (b) Negative edge-triggered Un Flip-Flop J-K es versátil y es uno de los tipos de Flip-Flop más utilizados, el funcionamiento de este Flip-Flop es idéntico al de un S-R en las condiciones de operación SET, RESET y de permanencia en estado NO Cambio. La diferencia está en que el Flip-Flop J-K no tiene condición no válida como ocurre en el S-R . 1-Flip flop j k síncrono funcionamiento Tabla de verdad CLK J K Q(t-1) X X X Qt 0 0 Qt 0 1 0 1 0 1 1 1 Q/t D Q C Q D Q C Q Indicador de Entrada Dinámica

- 15. PRACTICAS ELECTRONICA DIGITAL I TESE Flip flop D Un Flip-Flop tipo D resulta muy útil cuando se necesita almacenar un único bit de datos (1 o 0). Si se añade un inversor a un Flip-Flop S-R obtenemos un Flip-Flop tipo D básico. 2. Construir un Flip Flop D con un JK Circuito electrónico Tabla de verdad flip flop D síncrono CLK D Q(t+1) 0 X Qt 1 0 0 1 1 1

- 16. PRACTICAS ELECTRONICA DIGITAL I TESE 3. Construir un flip flop T con un jk Circuito electrónico Tabla de verdad flip flop T (Tooggle) síncrono 3. Circuito Paralelo- Serie Con Flip Flops CLK T Q(t+1) X X Qt 0 Qt 1 Q/t

- 17. PRACTICAS ELECTRONICA DIGITAL I TESE Referencias: Electronica Digital Moderna Simulador Electronics Workbench