compuertas logicas

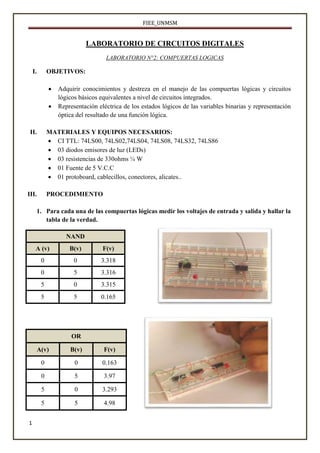

- 1. FIEE_UNMSM 1 LABORATORIO DE CIRCUITOS DIGITALES LABORATORIO N°2: COMPUERTAS LOGICAS I. OBJETIVOS: Adquirir conocimientos y destreza en el manejo de las compuertas lógicas y circuitos lógicos básicos equivalentes a nivel de circuitos integrados. Representación eléctrica de los estados lógicos de las variables binarias y representación óptica del resultado de una función lógica. II. MATERIALES Y EQUIPOS NECESARIOS: CI TTL: 74LS00, 74LS02,74LS04, 74LS08, 74LS32, 74LS86 03 diodos emisores de luz (LEDs) 03 resistencias de 330ohms ¼ W 01 Fuente de 5 V.C.C 01 protoboard, cablecillos, conectores, alicates.. III. PROCEDIMIENTO 1. Para cada una de las compuertas lógicas medir los voltajes de entrada y salida y hallar la tabla de la verdad. NAND A (v) B(v) F(v) 0 0 3.318 0 5 3.316 5 0 3.315 5 5 0.165 OR A(v) B(v) F(v) 0 0 0.163 0 5 3.97 5 0 3.293 5 5 4.98

- 2. FIEE_UNMSM 1 AND A(v) B(v) F(v) 0 0 0.171 0 5 0.167 5 0 0.162 5 5 4.981 XOR A(v) B(v) F(v) 0 0 0.167 0 5 3.339 5 0 3.361 5 5 0.174 NOT A(v) F(v) 0 3.348 5 0.162 NOR A(v) B(v) F(v) 0 0 3.270 0 5 0.171 5 0 0.171 5 5 0.156

- 3. FIEE_UNMSM 1 2. Implemente la función lógica OR utilizando solo compuertas NAND. Tabla de Verdad 1 Entradas Salida A1 (v) B1 (v) Led1 (v) 0 0 0.171 0 5 3.493 5 0 3.492 5 5 3.493 3. Implemente la función lógica AND utilizando solo compuertas NOR. Tabla de Verdad Entradas Salida A1 (v) B1 (v) Led1 (v) 0 0 0.171 0 5 0.172 5 0 0.171 5 5 3.449

- 4. FIEE_UNMSM 1 4. Implemente la función lógica XOR utilizando solo compuertas AND, OR y NOT. Tabla de Verdad Entradas Salida A1 (v) B1 (v) Led1 (v) 0 0 0.135 0 5 3.452 5 0 3.541 5 5 0.133 5. Implemente la función lógica XNOR utilizando solo compuertas AND, OR y NOT. Tabla de Verdad Entradas Salida A1 (v) B1 (v) Led1 (v) 0 0 3.449 0 5 0.141 5 0 0.141 5 5 3.452

- 5. FIEE_UNMSM 1 6. Para los pasos 2,3,4 y 5: a) Manipule el estado de las entradas y compruebe la tabla de la verdad. Los datos obtenidos manipulando las entradas fueron comprobada dos por la tabla de verdad teórica de dichas entradas, dichas tablas están en el paso anterior con los valores practicos obtenidos. b) Deduzca la expresión algebraica de la salida en función de la entrada. Para el OR: Para el AND: Para el XOR:

- 6. FIEE_UNMSM 1 Para el XNOR: V. CUESTIONARIO FINAL. 1) Presente y comente los datos resultantes obtenidos en base a los circuitos experimentados. Datos obtenidos del paso 1: NAND Practico Teórico OR Practico Teórico A (v) B(v) F(v) F(v) A (v) B(v) F(v) F(v) 0 0 3.318 5 0 0 0.163 0 0 5 3.316 5 0 5 3.97 5 5 0 3.315 5 5 0 3.293 5 5 5 0.165 0 5 5 4.98 5 AND Practico Teórico XOR Practico Teórico A (v) B(v) F(v) F(v) A (v) B(v) F(v) F(v) 0 0 0.171 0 0 0 0.167 0 0 5 0.167 0 0 5 3.339 5 5 0 0.162 0 5 0 3.361 5 5 5 4.981 5 5 5 0.174 0 NOR Practico Teórico NOT Practico Teórico A (v) B(v) F(v) F(v) A (v) F(v) F(v) 0 0 3.270 5 0 3.348 5 0 5 0.171 0 5 0 0.171 0 5 0.162 0 5 5 0.156 0

- 7. FIEE_UNMSM 1 Se supone que si estamos trabajando con circuitos integrados TTL que se alimentan con +5 voltios, el "1" se supondría que tiene un voltaje de +5 voltios y el "0" voltios. Esto es así en un análisis ideal de los circuitos digitales. En la realidad, estos valores son diferentes. Los circuitos integrados trabajan con valores de entrada y salida que varían de acuerdo a la tecnología del circuito integrado. En las tablas obtenidas se puede ver que los niveles de voltaje no son 5v pero están en un rango de valores donde se acepta un nivel alto o bajo (sea este "0" o "1"). En las compuertas TTL un nivel lógico de "1", será interpretado como tal, mientras el voltaje de la entrada esté entre 2 y 5 Voltios, y bajo si esta entre 0 y 0.8 voltios. Datos obtenidos del paso 2: Tabla N°1 Practico Teórico Tabla N°2 Practico Teórico A (v) B(v) F(v) F(v) A (v) B(v) F(v) F(v) 0 0 0.171 0 0 0 0.171 0 0 5 3.493 5 0 5 0.172 0 5 0 3.492 5 5 0 0.171 0 5 5 3.493 5 5 5 3.449 5 Tabla N°3 Practico Teórico Tabla N°4 Practico Teórico A (v) B(v) F(v) F(v) A (v) B(v) F(v) F(v) 0 0 0.135 0 0 0 3.449 5 0 5 3.452 5 0 5 0.141 0 5 0 3.541 5 5 0 0.141 0 5 5 0.133 0 5 5 3.452 5 Igualmente como es explico anteriormente los voltajes no son 5v por las pérdidas de voltaje del circuito integrado TTL, en este paso se pudo comprobar la expresión algebraica obtenida en el paso 6b, además de comprobar la forma booleana del XNOR y XOR en las tablas 4 y 3. 2) Observaciones y conclusiones. En esta práctica se observó el comportamiento de las compuertas NOT (inversor), AND (multiplicador), OR (sumador), NOR (sumador con salida invertida), NAND (sumador con salida invertida) y la XOR (que a su salida tendremos un 1 lógico cuando sus dos entradas son distintas), se apreció mediante circuitos combinacionales y LEDS a la salida, las diferentes cualidades de las compuertas, consiguiendo los resultados esperados por el laboratorio.

- 8. FIEE_UNMSM 1 Comprobamos que los circuitos integrados que utilizamos para la práctica cumplen con los parámetros de voltaje que se da en la tabla de la introducción teórica al experimentar en que momento deja de dar uno lógico y pasa a ser cero Las compuertas lógicas son los dispositivos electrónicos más sencillos que existen, pero al mismo tiempo son los más utilizados en la actualidad. VI. CONCLUSIONES Y RECOMENDACIONES Según la combinación de 0 y 1 que haya en las entradas de las puertas lógicas, la salida saldrá a 0 o a 1 dependiendo de la puerta. En una puerta AND, actúa como un multiplicador, entonces para que salga 1 a la salida han de estar las dos entradas a 1. ( 1 1=1 , 1 0=0 ) En una puerta OR, actúa como un sumador, entonces para que haya un 1 a la salida ha de estar una o dos de sus entradas a 1. ( 1+0=1 , 1+1=1 ) En las puertas NAND o NOR, las salidas actúan al contrario que las AND y OR, en otras palabras son sus negaciones. La compuerta XNOR y XOR son compuertas compuestas por otras compuertas lógicas, como se vio en el paso 2, actuando el XNOR como la negación del XOR. VII. BIBLIOGRAFIA Sistemas Digitales - Ronald J. Tocci Sistemas Electrónicos Digitales - Enrique Mandado Perez Fundamentos de Sistemas Digitales - Thomas L. Floyd