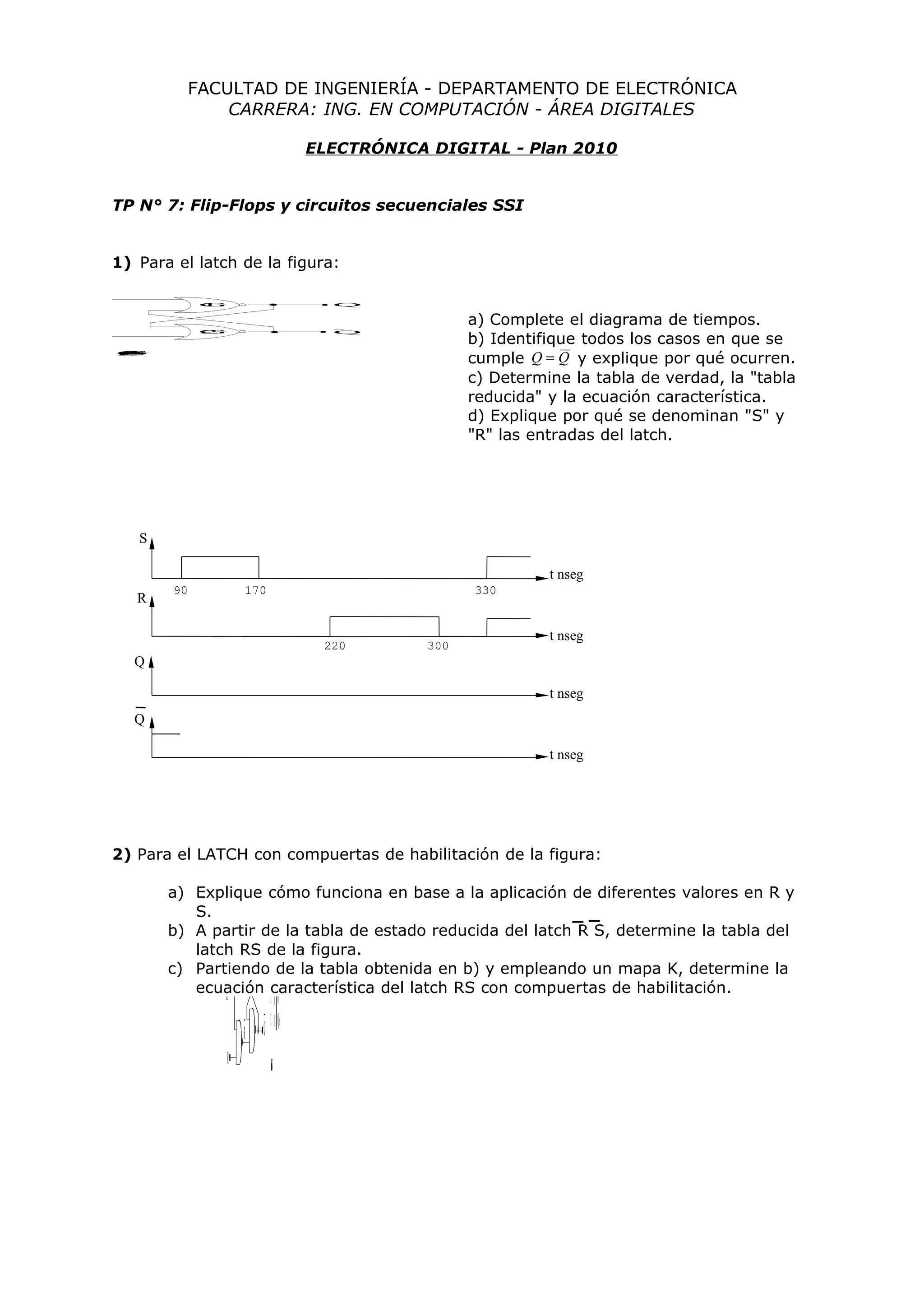

Este documento presenta una guía de ejercicios sobre circuitos secuenciales digitales como latches, flip-flops y monostables. Incluye preguntas sobre el funcionamiento y análisis de latches RS y latches con compuertas de habilitación, flip-flops D, T, JK, AB y CD, monostables 555 y 74121, y osciladores basados en estos circuitos. Se pide determinar tablas de estado, ecuaciones características, diagramas de tiempos y formas de onda, y diseñar circuitos para aplicaciones especí