Circuitos secuenciales síncronos

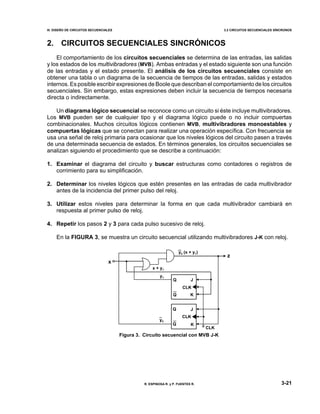

- 1. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-21 R. ESPINOSA R. y P. FUENTES R. 2. CIRCUITOS SECUENCIALES SINCRÓNICOS El comportamiento de los circuitos secuenciales se determina de las entradas, las salidas y los estados de los multivibradores (MVB). Ambas entradas y el estado siguiente son una función de las entradas y el estado presente. El análisis de los circuitos secuenciales consiste en obtener una tabla o un diagrama de la secuencia de tiempos de las entradas, salidas y estados internos. Es posible escribir expresiones de Boole que describan el comportamiento de los circuitos secuenciales. Sin embargo, estas expresiones deben incluir la secuencia de tiempos necesaria directa o indirectamente. Un diagrama lógico secuencial se reconoce como un circuito si éste incluye multivibradores. Los MVB pueden ser de cualquier tipo y el diagrama lógico puede o no incluir compuertas combinacionales. Muchos circuitos lógicos contienen MVB, multivibradores monoestables y compuertas lógicas que se conectan para realizar una operación específica. Con frecuencia se usa una señal de reloj primaria para ocasionar que los niveles lógicos del circuito pasen a través de una determinada secuencia de estados. En términos generales, los circuitos secuenciales se analizan siguiendo el procedimiento que se describe a continuación: 1. Examinar el diagrama del circuito y buscar estructuras como contadores o registros de corrimiento para su simplificación. 2. Determinar los niveles lógicos que estén presentes en las entradas de cada multivibrador antes de la incidencia del primer pulso del reloj. 3. Utilizar estos niveles para determinar la forma en que cada multivibrador cambiará en respuesta al primer pulso de reloj. 4. Repetir los pasos 2 y 3 para cada pulso sucesivo de reloj. En la FIGURA 3, se muestra un circuito secuencial utilizando multivibradores J-K con reloj.

- 2. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-22 R. ESPINOSA R. y P. FUENTES R. 2.1. CIRCUITOS SECUENCIALES SINCRÓNICOS 2.1.1. Modalidad de reloj El siguiente diagrama muestra el algoritmo de diseño y análisis de los circuitos secuenciales síncronos en la modalidad de reloj. Ejemplo de análisis: 1. Deducir la función del siguiente circuito: La ecuación de estado para el MVB J-K es: . . . . . . . . . . . . . . . (I) . . . . . . . . . . (II) . . . . . . . . . . (III) Del circuito se tiene: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . (1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . (2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . (3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . (4) Sustituyendo (1) y (2) en (II): . . . . . . . . . (5) Sustituyendo (3) y (4) en (III): . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . (6) De las ecuaciones (5) y (6), se obtienen las mascarillas para las tablas de estados. Utilizando mapas de K:

- 3. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-23 R. ESPINOSA R. y P. FUENTES R. Tablas de estados (asignando 00=q0 , 01=q1 , 11=q2 y 10=q3 ): y1 y0 x = 0 x = 1 y1 y0 qv x=0 x=1 y1 y0 qv x=0 x=1 0 0 1 1 0 1 1 0 0 0 1 0 0 0 1 0 0 1 1 1 1 0 1 1 0 0 1 1 0 1 1 0 q0 q1 q2 q3 q0 q0 q2 q0 q1 q3 q2 q2 0 0 1 1 0 1 1 0 q0 q1 q2 q3 q0,0 q0,0 q2,0 q0,0 q1,0 q3,0 q2,0 q2,1 Función: Circuito detector de secuencia con restauración externa con código 111 (en el tercer pulso Z=1). Ejemplo de diseño Se debe diseñar un circuito secuencial en la modalidad de reloj, que cuente con un mecanismo externo de restauración que, cuando sea necesario, deberá restaurar al circuito al estado inicial. Determinar un diagrama de estados del circuito, de tal manera que genere una salida 1 para un período de reloj que coincida sólo con la segunda entrada de 0 de una secuencia que se compone exactamente de 2 unos (no más de 2) seguidos por 2 ceros. Cuando la salida ha

- 4. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-24 R. ESPINOSA R. y P. FUENTES R. sido 1 durante un período de reloj, la salida se mantendrá en 0 hasta que el circuito se restaure exactamente. Diagrama de bloques. Carta de Tiempo. Diagrama de estados. Tabla de estados. qv x=0 x=1 q0 q1 q2 q3 q4 q5 q5,0 q5,0 q3,0 q4,1 q4,0 q5,0 q1,0 q2,0 q5,0 q3,0 q4,0 q1,0 Uno de los métodos de reducción de las tablas de estados es el método por inspección, el cual establece que dos estados son equivalentes si: 1. Son circuitos completamente especificados. Se dice que un circuito es completamente especificado, si partiendo de un estado se conoce a donde llegar (estado siguiente) y se sabe el valor de la señal de salida con un determinado vector de entrada. 2. Si de 8(q, x) = 8(p, x), se tiene que q = p. Donde: 8 = función de salida p, q = estados presentes x = vector de entrada Por lo tanto, se conoce que q0 y q5 son estados equivalentes; si cumplen con esta regla se puede anular a cualquiera de los dos. En este ejemplo se eliminará q5 , sustituyendolo en todos los casos por q0 .

- 5. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-25 R. ESPINOSA R. y P. FUENTES R. Tabla reducida. qv x=0 x=1 q0 q1 q2 q3 q4 q0,0 q0,0 q3,0 q4,1 q4,0 q1,0 q2,0 q0,0 q0,0 q4,0 Asignación de estados. Si: m = número de estados = 5 r = número de variables de estado = 2r > m r = número de multivibradores = 23 > 5 Como 8>5, entonces se tienen 3 variables de estado: y2, y1, y0. De lo anterior, se tiene la siguiente tabla de asignación de estados: y2 y1 y0 q1v q2v q3v q4v 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 q0 q1 q2 q3 q4 x x x x q0 q1 q2 q3 q4 x x x x q0 q1 q2 q3 q4 x x x x q0 q1 q2 q3 q4 Tomando en cuenta la primera. asignación (qv ), se obtiene la tabla asignada: qv y2 y1 y0 x=0 x=1 q0 q1 q2 q3 q4 x x x 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 000,0 000,0 010,0 110,1 110,0 xxx,x xxx,x xxx,x 001,0 011,0 000,0 000,0 110,0 xxx,x xxx,x xxx,x

- 6. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-26 R. ESPINOSA R. y P. FUENTES R. Utilizando multivibradores tipo J-K, cuya tabla de estados es: Q Q+ J K 0 0 1 1 0 1 0 1 0 1 x x x x 1 0 Obtención de los mapa K El logigrama queda: Ejemplo de diseño: Se debe diseñar un circuito secuencial de dos líneas de entrada x1 y x2 y una sola salida z. Si un pulso de reloj llega cuando x1=0 y x2=0 (00), el circuito debe asumir un estado de restauración que se puede representar con Q0. Suponer que los siguientes seis pulsos del reloj, después de un pulso de restauración, coinciden con la siguiente secuencia de combinaciones de entrada. Las entradas son 01, 10, 11, 01, 10 y 11. La salida z=1 coincidiendo con el sexto pulso de esta secuencia de 6 pulsos de reloj, pero z=0 en todos los otros momentos. El circuito no se puede restaurar a Q0 excepto mediante la entrada 00. Definir un estado especial al que puede pasar el circuito una vez que sea imposible que se produzca una secuencia que origine una salida. Por lo tanto, el circuito deberá esperar en el estado especial hasta que se restaure.

- 7. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-27 R. ESPINOSA R. y P. FUENTES R. Secuencia: 01, 10, 11, 01, 10, 11 Carta de tiempo: Diagrama de estados: TABLA DE ESTADOS TABLA REDUCIDA (q6 = q7 ) qv 0 0 0 1 1 1 1 0 qv 0 0 0 1 1 1 1 0 q0 q1 q2 q3 q4 q5 q6 q7 q0,0 q0,0 q0,0 q0,0 q0,0 q0,0 q0,0 q0,0 q1,0 q7,0 q7,0 q4,0 q7,0 q7,0 q7,0 q6,0 q7,0 q7,0 q3,0 q7,0 q7,0 q6,1 q7,0 q7,0 q7,0 q2,0 q7,0 q7,0 q5,0 q7,0 q7,0 q7,0 q0 q1 q2 q3 q4 q5 q6 q0,0 q0,0 q0,0 q0,0 q0,0 q0,0 q0,0 q1,0 q6,0 q6,0 q4,0 q6,0 q6,0 q6,0 q6,0 q6,0 q3,0 q6,0 q6,0 q6,1 q6,0 q6,0 q2,0 q6,0 q6,0 q5,0 q6,0 q6,0

- 8. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-28 R. ESPINOSA R. y P. FUENTES R. Diagrama de estados reducido: Uno de los criterios de asignación, es considerar al circuito de salida de tal manera que sea éste el más sencillo. Para conseguir esto, se mueve el estado q5 (en este caso) que contenga la señal de salida igual con 1, a una posición tal que sea fácil de hacer enlaces con los estados opcionales. qv 0 0 0 1 1 1 1 0 q0 q1 q2 q3 q4 q6 q5 qx q0,0 q0,0 q0,0 q0,0 q0,0 q0,0 q0,0 x,x q1,0 q6,0 q6,0 q4,0 q6,0 q6,0 q6,0 x,x q6,0 q6,0 q3,0 q6,0 q6,0 q6,0 q6,0 x,x q6,0 q2,0 q6,0 q6,0 q5,0 q6,0 q6,0 x,x Utilizando multivibradores tipo D, se pasa a la siguiente tabla: qv y2 y1 y0 0 0 0 1 1 1 1 0 q0 q1 q2 q3 q4 q6 q5 qx 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 x x x 1 1 1 1 1 1 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 x x x 1 1 1 0 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 x x x

- 9. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-29 R. ESPINOSA R. y P. FUENTES R. Mapas de Karnaugh:

- 10. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-30 R. ESPINOSA R. y P. FUENTES R. El logigrama correspondiente es: EJERCICIOS 1. Determinar el diagrama y la tabla de estados de un circuito detector de secuencia que detecte 101. La salida debe ser 1 cuando ocurra el último pulso de la secuencia. La salida Z deberá restablecerse a 0 para el siguiente pulso. La secuencia deberá presentar traslape. x = 010101101 2. Obtener el diagrama y la tabla de estados para un detector de secuencia de tal manera que Z = 1 en el segundo bit de 2 unos consecutivos. El circuito puede diseñarse con traslape siempre y cuando se siga la siguiente secuencia: x = 01100111110

- 11. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-31 R. ESPINOSA R. y P. FUENTES R. 3. Obtener el diagrama y la tabla de estados tal que Z = 1 cuando ocurra el segundo bit de la secuencia 01. x = 010100100 4. Obtener la tabla y el diagrama de estados tal que Z = 1 cuando la secuencia sea 1010. x = 00101001010101110 5. En una intersección de dos calles, una en la dirección norte-sur (NS) y otra en la este-oeste (EO). Se instalan semáforos con indicaciones de rojo, ámbar y verde. Diseñar un circuito mostrando la secuencia de estados que recorrerán las luces. Suponer que el sistema está controlado por un reloj cuyo período es de 5 segundos. En cada dirección se permite tráfico durante 20 segundos y la luz ámbar dura 20 segundos. REDUCCIÓN DE TABLAS DE ESTADO Existen tres métodos: Por inspección, por particiones y por tablas de implicación. Método de reducción por particiones. Definiciones: RELACIÓN DE EQUIVALENCIA: Cuando un par de ordenadas de elementos x,y posee una propiedad que los relaciona, se dice que x está relacionado con y. x R y Para que se cumpla la expresión anterior, se requiere: 1. x R y entonces x = x reflexiva. 2. x R y entonces x = y simétrica. 3. x R y y y R z entonces x = y y y = z, por tanto: x = z transitiva. ESTADOS EQUIVALENTES: La condición para que existan estados equivalentes, es que el circuito esté completamente especificado. Se dice que un circuito está completamente especificado si las salidas y los estados siguientes se especifican para cada combinación de estados presentes y de entrada.

- 12. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-32 R. ESPINOSA R. y P. FUENTES R. La función de estado siguiente se denota por el símbolo * y la función de salida por 8. Notación: * = Estado presente, vector de entrada = qv+1 8 = Estado siguiente, vector de salida = Z Ejemplo: Sea la siguiente tabla y el vector x = 023001: q x 0 1 3 2 q1 q2 q3 q4 q3,0 q3,0 q3,0 q4,0 q1,0 q3,0 q1,1 q4,0 q2,0 q4,0 q1,3 q2,0 q2,0 q4,0 q1,2 q2,0 *(q1,0 ) = q3 8(q1,0 ) = 0 = 00 *(q3,2 ) = q1 8(q3,2 ) = 2 = 10 *(q1,3 ) = q2 8(q1,3 ) = 0 = 00 *(q2,0 ) = q3 8(q2,0 ) = 0 = 00 *(q3,0 ) = q3 8(q3,0 ) = 0 = 00 *(q3,1 ) = q1 8(q3,0 ) = 1 = 01 De lo anterior, se pueden establecer las siguientes definiciones: DEFINICIÓN 1: Sean A y B dos circuitos completamente especificados sujetos a las mismas secuencias de entrada posibles: Sea x1, x2,..., xm una secuencia de valores posibles del conjunto de entrada x de una longitud arbitraria. Los estados p0B y q0A son indistinguibles (equivalentes), lo cual se expresa como p = q si y sólo si: 8A(q,x1,x2,x3,...,xm) = 8B(p,x1,x2,x3,...,xn) DEFINICIÓN 2: Se dice que los circuitos secuenciales A y B son equivalentes, lo cual se expresa A = B, si para cada estado q0A, existe una tabla de estado p0B, tal que p = q, e inversamente para cada estado p0B existe un estado q0A, tal que q = p. CONCLUSIÓN: Dada una tabla de estados, el objetivo es obtener una tabla de estados con el menor número posible de ellos, porque esto implica utilizar un número menor de elementos de memoria (multivibradores). DEFINICIÓN 3: Se hará que los estados de un circuito secuencial se dividan en clases separadas. p = q denota que los estados p y q queden dentro de la misma clase en la partición. Esta partición se compone de clases de equivalencia de estados indistinguibles (2 estados indistinguibles deben estar en la misma clase), si y sólo si se satisfacen las 2 condiciones siguientes para cada par de estados p y q en la misma clase (p = q) y cada entrada individual x: 1. 8(p,x) = 8(q,x) Indica que las salidas son iguales 2. *(p,x) = *(q,x) Significa que quedan dentro de la misma clase Ejemplo: Dada la siguiente tabla, reducirla por el método de particiones.

- 13. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-33 R. ESPINOSA R. y P. FUENTES R. qv x=0 x=1 1 2 3 4 5 6 7 1,0 1,1 4,0 1,1 2,0 4,0 2,0 1,0 6,1 5,0 7,0 3,0 5,0 3,0 a b a c a a a Clase a: Son todos los estados que para x=0 y x=1, la salida es cero Clase b: Son todos los estados que para x=0 y x=1, la salida es uno Clase c: Son todos los estados que para x=0, z=1 y para x=1, z=0 1ª. Parte: 2ª. Parte: (1ª partición) CLASE ESTADOS CLASE a b c a b c 1,3,5,6,7 2 4 qv qv+1 1 3 5 6 7 aa ca ba ca ba 2 aa 4 aa 2ª partición CLASE ESTADOS CLASE a b c d e a b c d e 1 2 4 3,6 5,7 qv qv+1 1 aa 2 ad 4 ae 3 6 ce ce 5 7 bd bd Se elimina 5 y 7 por se equivalentes con 3 y 5 Tabla reducida: qv x=0 x=1 1 2 3 4 5 1,0 1,1 4,0 1,1 2,0 1,0 3,1 5,0 5,0 3,0

- 14. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-34 R. ESPINOSA R. y P. FUENTES R. EJERCICIOS: Dadas las siguientes tablas, reducirlas por el método de reducciones: 1. 2. 3. qv x=0 x=1 qv x=0 x=1 qv x=0 x=1 1 2 3 4 5 6 7 1,0 1,0 4,1 2,0 1,0 3,1 2,0 1,1 6,1 5,1 6,0 3,1 4,0 3,0 q0 q1 q2 q3 q4 q5 q6 q7 q0,1 q0,0 q1,0 q1,0 q2,0 q2,0 q3,0 q3,0 q0,0 q4,0 q5,0 q5,0 q6,1 q6,1 q7,1 q7,1 q0 q1 q2 q3 q4 q5 q6 q7 q1,0 q0,1 q2,0 q5,0 q1,1 q3,1 q2,1 q2,1 q0,1 q3,1 q4,0 q2,1 q6,0 q5,0 q7,0 q7,0 Método de reducción por tablas de implicación. Un conjunto de estados P se implica mediante un conjunto de estados R si para cada entrada específica x, P es el conjunto de todos los estados siguientes *(r,x), para todos los estados presentes r en R. Ejemplo: qv x=0 x=1 qv 0 1 2 3 1 2 3 4 5 6 7 8 9 10 11 12 2,0 4,0 6,0 8,0 10,0 4,0 10,0 8,0 10,1 4,0 2,0 2,0 3,0 5,0 7,0 9,0 1,0 12,0 12,0 1,0 1,0 1,0 1,0 1,0 1 2 3 4 3 4 1 1 4 4 1 2 2 3 3 1 4 4 4 4

- 15. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-35 R. ESPINOSA R. y P. FUENTES R. 2 2-4 3-5 3 2-6 3-7 4-6 5-7 4 2-8 3-9 4-8 5-9 6-8 7-9 5 2-10 1-3 4-10 1-5 6-10 1-7 6-8 7-9 6 2-4 3-12 5-12 4-6 7-12 4-8 9-12 4-10 1-12 7 2-10 3-12 4-10 5-12 6-10 7-12 8-10 9-12 1-12 4-10 8 2-8 3-1 4-8 1-5 6-8 1-7 1-9 8-10 4-8 1-12 8-10 1-12 9 10 2-4 1-3 1-5 4-6 1-7 4-8 1-9 4-10 1-12 4-10 1-12 4-8 11 2-2 1-3 2-4 1-5 4-6 1-7 4-8 1-9 2-10 2-4 1-12 2-10 1-12 2-8 2-4 12 1-3 2-4 1-5 2-6 1-7 2-8 1-9 2-10 2-4 1-12 2-10 1-12 2-8 2-4 U ³ significa que ya está implicado (en el 10) 1 2 3 4 5 6 7 8 9 10 11 Pasos eliminados: 1er. Paso: 1-9, 2-9, 3-9, 4-9 5-9, 6-9, 7-9, 8-9, 9-10, 9-11, 9-12 Para el segundo paso se eliminan todos los que tengan implicados los del primer paso. 2do. Paso: 1-4, 2-4, 3-4, 4-5, 4-6, 4-7, 4-8, 4-10, 4-11, 4-12 3er. Paso: 1-2, 1-6, 1-10, 2-3, 2-5, 2-7, 2-8, 2-11, 3-6, 3-10, 5-6, 5-10, 6-7, 6-8, 6-11, 6-12, 7-10, 8-10, 10-11, 10-12 4to. Paso: 1-8, 3-8, 5-8, 7-8, 8-11, 8-12 Búsqueda de pares equivalentes:

- 16. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-36 R. ESPINOSA R. y P. FUENTES R. 11 10 9 8 7 6 5 4 3 2 1 (11-12) (11-12) (11-12) (11-12) (11-12)(7-11)(7-12) (11-12)(7-11)(7-12)(6-10) (11-12)(7-11)(7-12)(6-10)(5-7)(5-11)(5-12) (11-12)(7-11)(7-12)(6-10)(5-7)(5-11)(5-12) (11-12)(7-11)(7-12)(6-10)(5-7)(5-11)(5-12)(3-5)(3-7)(3-11)(3-12) (11-12)(7-11)(7-12)(6-10)(5-7)(5-11)(5-12)(3-5)(3-7)(3-11)(3-12)(2-6)(2-10) (11-12)(7-11)(7-12)(6-10)(5-7)(5-11)(5-12)(3-5)(3-7)(3-11)(3-12)(2-6)(2-10)(1-3)(1-)(1-7)(1-11)(1-12)(4)(8)(9) Diagrama de Merger: TABLA REDUCIDA qv x = 0 x = 1 1 2 4 8 9 2,0 4,0 8,0 8,0 2,1 1,0 1,0 9,0 1,0 1,0

- 17. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-37 R. ESPINOSA R. y P. FUENTES R. EJERCICIOS Reducir por medio de tablas de implicación: 1. 2. 00 01 10 11 00 01 10 11 00 01 10 11 qv 0 1 2 3 0 1 2 3 qv 0 1 2 3 1 2 3 4 5 6 7 8 9 10 11 6 6 6 5 5 6 5 6 9 6 6 2 3 9 6 9 6 10 2 9 11 9 1 1 4 7 7 1 7 1 1 1 4 1 1 1 8 1 1 1 8 1 1 1 0 0 0 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 A B C D E F G H E,1 C,0 B,1 G,0 C,0 C,1 D,1 B,1 C,0 F,1 A,0 F,1 F,1 F,1 A,0 C,0 B,1 E,1 D,1 E,1 D,1 D,0 B,1 E,1 E,1 B,0 F,1 B,0 E,0 H,0 F,1 F,1 ASIGNACIÓN DE ESTADOS: El número total de elementos de memoria MFF = r = variables de estado, está relacionado al número de estados NS = m del circuito, es decir: Por lo tanto, habrá un número de asignación de estados, NAE, igual a: Que es la forma de asignación de estados de 2r combinaciones de estados binarios de asignación a los NS (m) estados. La siguiente tabla muestra algunos ejemplos numéricos:

- 18. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-38 R. ESPINOSA R. y P. FUENTES R. NÚMERO DE ESTADOS (m) NÚMERO DE VARIABLES DE ESTADO (r) NÚMERO DE ASIGNACIONES DE ESTADO (NAE) NÚMERO DE ASIGNACIONES ESPECÍFICAS 1 2 3 4 5 6 7 8 9 10 0 1 2 2 3 3 3 3 4 4 - 2 24 24 6,720 20,160 40,320 40,320 4.5x109 4.9x1010 . 3 3 3 140 420 840 840 10'810,800 75'675,600 Asignaciones útiles: Criterios para la asignación de estados: Regla I A) Se deben examinar los renglones de la tabla reducida que tengan anotaciones idénticas para el estado siguiente en cada columna. Estos renglones deben recibir asignaciones adyacentes. De ser posible las anotaciones del estado siguiente en esos renglones deben recibir asignaciones de acuerdo con la regla II. B) Se verifican los renglones de la tabla de estados reducida que tienen las mismas anotaciones del estado siguiente pero en diferente orden de columna. A estos renglones se les debe dar asignaciones adyacentes, Las anotaciones del estado siguiente pueden recibir asignaciones adyacentes. C) Los renglones con anotaciones idénticas para el estado siguiente, en algunas pero no en todas las columnas, deben recibir asignaciones adyacentes, en donde los renglones que tengan más columnas idénticas asuman la máxima prioridad. Regla II Las anotaciones del estado siguiente para un renglón dado, deben recibir asignaciones diferentes. Regla III Las asignaciones deben hacerse de tal manera que simplifiquen los mapas de salida. Ejemplo: El principio de un mensaje de un sistema de sistema de comunicación en particular, se denota mediante la aparición de 3 unos consecutivos en una línea x. Los datos en esta línea se han sincronizado con una señal de reloj que tenga una salida 1 sólo en el tiempo de reloj que coincida

- 19. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-39 R. ESPINOSA R. y P. FUENTES R. con el tercero de una secuencia de 3 unos en la línea x. El circuito servirá para advertirle al sistema receptor sobre la iniciación de un mensaje. Se propone un mecanismo de restauración independiente una vez que concluya el mensaje. CARTA DE TIEMPO DIAGRAMA DE ESTADOS TABLA REDUCIDA q(V) x = 0 x = 1 q(V) x = 0 x = 1 q0 q1 q2 q3 q4 q4,0 q4,0 q4,0 q3,0 q4,0 q1,0 q2,0 q3,1 q3,0 q1,0 a a b a q0 = q4 q0 q1 q2 q3 q0,0 q0,0 q0,0 q3,0 q1,0 q2,0 q3,1 q3,0 1a. Asignación utilizando MVB tipo J-K q(V) y1 y0 x=0 x=1 Q Q+ J K q0 q1 q2 q3 0 0 0 1 1 1 1 0 00,0 00,0 00,0 10,0 01,0 11,0 10,1 10,0 0 0 1 1 0 1 0 1 0 1 x x x x 1 0

- 20. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.2 CIRCUITOS SECUENCIALES SÍNCRONOS 3-40 R. ESPINOSA R. y P. FUENTES R. 2a. Asignación q(V) y1 y0 x=0 x=1 q0 q1 q2 q3 0< 0 0 1 1 1 1 0 00,0 00,0 00,0 10,0 11,0 10,0 01,0 10,0 3a. Asignación q(V) y1 y0 x=0 x=1 q0 q1 q2 q3 0 0 0 1 1 1 1 0 00,0 00,0 11,0 00,0 10,0 11.1 11,0 01,0

- 21. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-41 R. ESPINOSA R. y P. FUENTES R. 3. CIRCUITOS SECUENCIALES ASÍNCRONOS 3.1Modalidad de pulso Un circuito secuencial se dice estar operando en la modalidad de pulso si se satisfacen las siguientes condiciones: A. Al menos una de las señales de entrada es un pulso. B. Los cambios de los estados internos ocurre únicamente en respuesta a ala ocurrencia de un pulso en las terminales de entrada. C. Cada estado de entrada, con la ocurrencia de un pulso, origina únicamente un cambio en el estado interno. D. Todas las entradas de pulso deberán ser lo suficientemente amplio para disparar un multivibrador (MVB). E. Todos los MVB serán asíncronos o de los síncronos pero disparados por flancos o de los determinados maestro-esclavo. F. En las entradas no se permite la ocurrencia de dos o más pulsos en forma simultánea. G. Las tablas de estados tendrán tantas columnas como pulsos de entrada existan. H. En los mapas de Karnaugh no es válido hacer enlaces horizontales, sólo se permiten enlaces verticales. I. Existen dos tipos de pulsos en esta modalidad: Mealy y Moore. J. Un circuito de Mealy es aquel cuyas entradas y salidas son un pulso. Como puede observarse del modelo adjunto, un circuito de Mealy consta de dos circuitos combinacionales, el primero maneja las señales de memoria y el segundo las salidas. Las señales de salida dependen no solamente de los pulsos de entrada sino también de los estados presentes. K. Un circuito de Moore es aquel cuyas entradas son pulsos y las señales de salida son de nivel.

- 22. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-42 R. ESPINOSA R. y P. FUENTES R. En un circuito de Moore, figura adjunta, las señales de salida corresponden exclusivamente a los estados presentes. Es importante tener siempre en cuenta que las señales de entrada de un sistema secuencial pueden ser de dos tipos: NIVEL:El estado de entrada y/o salida varía de un valor a otro sin problemas de continuidad. IMPULSO: Entre dos estados de entrada diferentes existe un estado inactivo en el cual todas las variables toman el valor lógico cero. EJEMPLO: Determinar los diagramas de estados de los circuitos de Mealy y Moore, cuando se tiene una secuencia x1x2x3 y la salida es 1 en el último pulso, es decir: Secuencia: x1x2x3 Salida: z = 0 0 1 SOLUCIÓN Tabla de estados q(V) x1 x2 x3 q0 q1 q2 q3 q1,0 q2,0 q2,0 q2,1 q2,0 q3,0 q2,0 q2,0 q0,0 q0,0 q0,0 q0,0

- 23. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-43 R. ESPINOSA R. y P. FUENTES R. Tabla de estados q(V) x1 x2 x3 z q0 q1 q2 q3 q4 q1 q2 q2 q4 q2 q2 q3 q2 q2 q2 q0 q0 q0 q0 q0 0 0 0 0 1 x x x opcionales para los mapas EJEMPLO: Un ciclo de un sistema digital está compuesto de tres subciclos que deben completarse en un cierto orden. Para comprobar esto, un verificador de secuencia recibirá un pulso de terminación de cada subciclo y un pulso de verificación cuando el ciclo principal haya concluido. Cuando llega el pulso de verificación K el verificador de secuencia llega a restaurarse y emitir un pulso de error, si los tres pulsos de terminación A, B y C no se recibieron es ése orden. Existen 6 secuencias posibles: ABC K Z = 0 ACB K Z = 1 BAC K Z = 1 BCA K Z = 1 CAB K Z = 1 CBA K Z = 1 Tabla de estados q(V) A B C K q0 q1 q2 q3 q4 q1,0 -,- -,- -,- q4,0 q4,0 q2,0 -,- -,- q4,0 q4,0 q4,0 q4,0 -,- q4,0 -,- -,- -,- q0,0 q0,1

- 24. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-44 R. ESPINOSA R. y P. FUENTES R. Por observación de la tabla de estados, decimos que se trata de un circuito incompletamente especificado. Por lo tanto, ahora no buscaremos estados equivalente, sino estados equivalentes. No son factibles: q0+ q1 , q0+ q2 , q0+ q4 , q1+ q2 , q1+ q4 , q2+ q3 , q2 , q4 , q3+ q4 q0+ q3 = q1,0 q4,0 q4,0 -,- q2+ q2 = -,- -,- q3,0 -,- -,- -,- -,- q0,0 -,- -,- -,- q0,0 q0 =q3 = q1,0 q4,0 q4,0 q0,0 q2 =q3 = -,- -,- q3,0 q0,0 q1+ q3 = -,- q2,0 q4,0 -,- -,- -,- -,- q0,0 q1 =q3 = -,- q2,0 q4,0 q0,0 Si se toma el que quedo completamente especificado (q0 = q3): Tabla reducida q(V) A B C R q0 q1 q2 q4 q1,0 -,- -,- q4,0 q4,0 q2,0 -,- q4,0 q4,0 q4,0 q0,0 q4,0 q0,0 -,- -,- q0,1 Nota: La tabla de estados reducida quedó de esta manera debido a que no existe q0 =q1 =q2 =q3 , se rompieron los lazos q16 q3 y q26 q3 y los 1, 2 y 4 quedaron como estados únicos. Asignación de estados Tabla de excitación de la tabla No Y q(V) y1 y0 A B C K Q Q+ S R q0 q1 q2 q4 0 0 0 1 1 1 1 0 01 XX XX 10 10 11 XX 10 10 10 00 10 00 XX XX 00,1 0 0 0 1 1 0 1 1 1 X 0 1 1 0 X 1

- 25. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-45 R. ESPINOSA R. y P. FUENTES R. Mapas de Karnaugh: El siguiente logigrama muestra el circuito verificador de secuencia: 3.2. Modo fundamental Las características para este tipo de circuito secuencial son: 1. J representa el tiempo de retardo mínimo para que ocurra una transición. Este tiempo de retardo es el que se obtiene cuando una señal viaja a través de una o más compuertas. Esto indica que la retroalimentación es directa. 2. La entrada y la salida son de nivel. 3. Con respecto a las variables de entrada, no puede haber dos cambios en forma simultánea. 4. Un estado estable es aquel cuyo valor del estado presente es igual al estado siguiente.

- 26. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-46 R. ESPINOSA R. y P. FUENTES R. 5. Cuando iniciamos un recorrido, al partir de un estado estable, siempre se realizan dos movimientos, uno horizontal y otro vertical. El primero se da cuando hay cambios en las señales de entrada y el segundo cuando partiendo de un estado estable se llega a un estado inestable, lo cual origina una búsqueda de un estado estable en ésa columna. 6. En el proceso de diseño de diseño, no se permite más de un estado estable por fila. 7. Las señales de salida son de nivel, por lo tanto, en el proceso de diseño, se tendrán tantas columnas como señales de salida existan. EJEMPLO: Diseñar un circuito que controle la barra de un estacionamiento público de autos compactos; el circuito debe ser totalmente automatizado. Consta de un receptor de monedas, un sensor infrarojo y un interruptor de piso. Lo anterior debe accionar en conjunto y en la secuencia que se especificará a una barra para controlar la entrada a dicho estacionamiento. Primero estará colocado el receptor de monedas, más adelante el receptor infrarojo y poco antes de llegar a la barra el interruptor de piso. Cuando se deposite una moneda o la cuota establecida, el auto avanzará hasta interrumpir el haz de luz, poco después la llanta delantera oprimirá por primera vez el interruptor de piso, el auto avanzara y oprimirá por segunda ocasión el interruptor de piso, el auto seguirá avanzando y dejará libre el haz de luz, con lo que completará un ciclo de funcionamiento. Cualquier otra eventualidad, podría ser que tratasen de entrar (uno tras otro), el interruptor de piso al detectar una tercera llanta, la barra bajará dañando al segundo auto; al interrumpir el haz de luz sin depositar la moneda, la barra no se levantará y cualesquier otros tipos de secuencias, que se salgan de lo establecido, serán nulas. DISEÑO El diagrama a bloques adjunto, esquematiza a los elementos del problema: Del diagrama se definen las siguientes variables y sus valores lógicos: Variables de entrada: M = Moneda 1 = Depositada F = Foto Celda 1 = Haz interrumpido S = Sensor de piso 1 = Sensor activado Variables de salida: Z = Barra 1= Barra arriba Tabla primitiva de flujo:

- 27. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-47 R. ESPINOSA R. y P. FUENTES R. Reducción de la tabla de estados: Pares encontrados 1-9 2-3 8-9 8-10 9-10 S S S S 1 2 3 4 5 6 7 8 9

- 28. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-48 R. ESPINOSA R. y P. FUENTES R. Diagrama de Meyer: Tabla reducida: 000 001 011 010 110 111 101 100 Z 1 - - - - - - 2 0 - - - - 2 4 - 2 1 - - - - 5 4 - - 1 - - - - 5 6 - - 1 - - - - 7 6 - - 1 - - - - 7 8 - 8 1 - - - - 8 8 - 8 1 Asignación de estados: qv Y3 Y2 Y1 000 001 011 010 110 111 101 100 1 2 4 5 6 7 8 X 0 0 0 0 1 1 1 1 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 000 xxx xxx xxx xxx xxx 000 xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx 001 010 010 111 111 101 xxx xxx 011 011 110 110 101 101 xxx xxx xxx xxx xxx xxx xxx xxx xxx 001 001 xxx xxx xxx 101 101 xxx

- 29. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-49 R. ESPINOSA R. y P. FUENTES R. Utilizando mapas de Karnaugh: El logigrama para Y3, Y2, Y1 y Z, es: EJEMPLO: El sistema que se desea diseñar debe controlar la acción de las barreras que permiten o impiden el paso de automóviles en un crucero de ferrocarril. La vía es única, los trenes pueden pasar en uno u otro sentido y la longitud de los convoyes es indistinto. Tres detectores a, b y c indican la presencia de un tren en diferentes posiciones y las variantes de salida de éstos (a, b y c respectivamente), toman un valor lógico 1 si hay un tren presente en la posición correspondiente. El vector b está colocado en el crucero, mientras a y c están dispuestos a diferentes distancias, a uno y otro lado de la intersección; supóngase que la distancia entre a y b es menor que entre b y c.

- 30. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-50 R. ESPINOSA R. y P. FUENTES R. DISEÑO Primeramente se analizarán las longitudes posibles a los trenes con respecto a los lugares o a las distancias en que están instalados los sensores, como se muestra en la siguiente figura: Tabla primitiva de flujo:

- 31. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-51 R. ESPINOSA R. y P. FUENTES R. De la tabla se obtiene: De la información anterior, se obtiene la siguiente tabla reducida: Asignación de estados: qv Y3 Y2 Y1 000 001 011 010 110 111 101 100 z 1 2 4 5 6 x x x 0 0 0 0 1 1 1 1 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 000 001 010 010 000 xxx xxx xxx 001 001 110 110 110 xxx xxx xxx xxx 011 011 xxx xxx xxx xxx xxx xxx 011 011 xxx xxx xxx xxx xxx xxx 011 011 xxx xxx xxx xxx xxx xxx xxx 011 xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx xxx 001 001 110 110 110 xxx xxx xxx 0 1 1 0 0 x x x

- 32. III. DISEÑO DE CIRCUITOS SECUENCIALES 3.3 CIRCUITOS SECUENCIALES ASÍNCRONOS 3-52 R. ESPINOSA R. y P. FUENTES R. Mapas de Karnaugh: El logigrama del crucero de ferrocarril es: