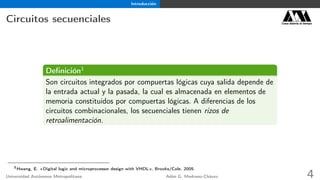

Este documento presenta información sobre circuitos secuenciales. Introduce conceptos como cerrojos, flip-flops, señales de reloj y simulación de elementos de memoria. El objetivo es que los estudiantes aprendan a diseñar procesadores de propósito específico usando circuitos que pueden almacenar información temporalmente como cerrojos y flip-flops.

![Arreglos de elementos de memoria Registros

Registros Casa abierta al tiempo

Implementación en Verilog

Para implementar un registro de n

bits, solo hay que parametrizar la

entrada d y salida de datos q de los

cerrojos y biestables a n bits, e.g. en

el código de la derecha se muestra un

registro de cerrojos tipo D

parametrizado a n bits.

1 module latch_d_reg (

2 d, //n-bit data input

3 q, //n-bit state output

4 enable // control input

5 );

6

7 parameter n = 8;

8

9 input wire[n -1:0] d;

10 input wire enable;

11 output reg[n -1:0] q;

12

13 // Behavioral description

14 always @(enable or d) begin

15 if (enable) begin

16 q <= d;

17 end

18 end

19

20 endmodule // latch_d

Universidad Autónoma Metropolitana Adán G. Medrano-Chávez 37](https://image.slidesharecdn.com/sequential-170730061318/85/Sequential-37-320.jpg)

![Arreglos de elementos de memoria Registros

Registros Casa abierta al tiempo

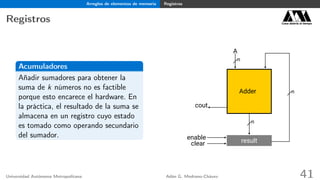

Acumuladores

Una operación importante realizada

por los sistemas digitales es la suma

de k números. El detalle de esta

operación es que, si se quiere

efectuarse en un paso, requiere de

k − 1 sumadores con propagación de

acarreo, e.g. la suma de a + b + c

requiere de dos sumadores.

FA FA FA FA FA FA FAFA

8a

ci

a[7] a[6] a[5] a[4] a[3] a[2] a[1] a[0]

a+b[7] a+b[6] a+b[5] a+b[4] a+b[3] a+b[2] a+b[1] a+b[0]

cout

b[7] b[6] b[5] b[4] b[3] b[2] b[1] b0]

FA FA FA FA FA FA FAFA

8c

ci

c[7] c[6] c[5] c[4] c[3] c[2] c[1] c[0]

s[7] s[6] s[5] s[4] s[3] s[2] s[1] s[0]cout

Universidad Autónoma Metropolitana Adán G. Medrano-Chávez 40](https://image.slidesharecdn.com/sequential-170730061318/85/Sequential-40-320.jpg)

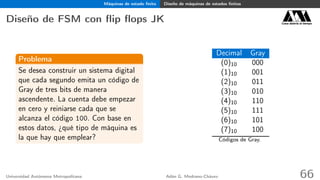

![Máquinas de estado finito Diseño de máquinas de estados finitos

Diseño de FSM con flip flops tabla Casa abierta al tiempo

Problema

Diseñe un contador ascendente/descendente que cuente en el rango

[−4, +3] con flip flops T. El contador debe poseer una entrada ctrl

que determina el sentido de la cuenta; si ctrl = 1, entonces la cuenta

es descendete, de lo contrario, la cuenta es ascendente.

Universidad Autónoma Metropolitana Adán G. Medrano-Chávez 74](https://image.slidesharecdn.com/sequential-170730061318/85/Sequential-74-320.jpg)