Circuitos Digitales - Contador Digital

•

1 recomendación•300 vistas

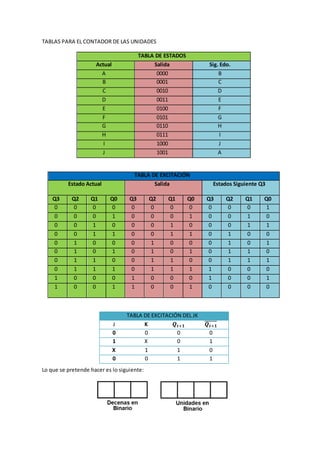

El documento describe los pasos para crear circuitos digitales que cuenten en binario hasta 9 y 5 para las unidades y decenas respectivamente. Incluye tablas de estados, excitación y Karnaugh para contadores JK de 4 bits y 3 bits que implementarán la funcionalidad deseada, así como los diagramas del circuito completo.

Denunciar

Compartir

Denunciar

Compartir

Recomendados

Recomendados

Más contenido relacionado

La actualidad más candente

La actualidad más candente (16)

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 1er Parcial (2020 PAO 1) B

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 1er Parcial (2020 PAO 1) B

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 1) C5 A

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 1) C5 A

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN FUNDAMENTOS DE ELECTRICIDAD Y SISTEMAS DIGITALES, M...

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN FUNDAMENTOS DE ELECTRICIDAD Y SISTEMAS DIGITALES, M...

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN FUNDAMENTOS DE ELECTRICIDAD Y SISTEMAS DIGITALES, 2...

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN FUNDAMENTOS DE ELECTRICIDAD Y SISTEMAS DIGITALES, 2...

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 1)

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 1)

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN FUNDAMENTOS DE ELECTRICIDAD Y SISTEMAS DIGITALES, Cap ...

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN FUNDAMENTOS DE ELECTRICIDAD Y SISTEMAS DIGITALES, Cap ...

Electrónica digital: sistemas secuenciales maquina de estado

Electrónica digital: sistemas secuenciales maquina de estado

Destacado

Destacado (20)

Presentación de diapositivas de manejo de tecnologia

Presentación de diapositivas de manejo de tecnologia

Tutorial para participar en un foro yuly pauline cardenas

Tutorial para participar en un foro yuly pauline cardenas

Similar a Circuitos Digitales - Contador Digital

Electrónica digital

Electrónica digital: Síntesis de circuitos secuenciales síncronos: Maquinas d...

Electrónica digital: Síntesis de circuitos secuenciales síncronos: Maquinas d...SANTIAGO PABLO ALBERTO

Asignacion Final de Circuito Digital y Microprocesador 20% Samuel Jose Movilio Diaz Ultima asignacion 20% circuito digital Samuel Movilio

Ultima asignacion 20% circuito digital Samuel Movilioinstituto universitario politecnico santiago mariño

Similar a Circuitos Digitales - Contador Digital (20)

Circuitos Digitales - Contador base 60 - Cronometro

Circuitos Digitales - Contador base 60 - Cronometro

Circuitos Digitales - Contador ascendente y descendente con reset

Circuitos Digitales - Contador ascendente y descendente con reset

D:\De Todo\Articulos William\DiseñO De Un Contador Con Flip Flops Tipo Jk

D:\De Todo\Articulos William\DiseñO De Un Contador Con Flip Flops Tipo Jk

Electrónica digital: Tema 7 Sistemas secuenciales síncronos

Electrónica digital: Tema 7 Sistemas secuenciales síncronos

Electrónica digital: Circuitos Secuenciales síncronos

Electrónica digital: Circuitos Secuenciales síncronos

Electrónica digital: Síntesis de circuitos secuenciales síncronos: Maquinas d...

Electrónica digital: Síntesis de circuitos secuenciales síncronos: Maquinas d...

Ultima asignacion 20% circuito digital Samuel Movilio

Ultima asignacion 20% circuito digital Samuel Movilio

Electrónica digital: capitulo 7 Autómatas finitos parte 2

Electrónica digital: capitulo 7 Autómatas finitos parte 2

Más de Fernando Marcos Marcos

Simulation:

https://youtu.be/rvsUvkgi8ro

Se diseño un circuito para lectura de temperatura utilizando el sensor LM35, la lectura se mostro mediante un multiplexor en 4 displays de siete segmentos (Ánodo y Cátodo Común), para el desarrollo del proyecto se utilizo la tarjeta Arduino Uno con el microcontrolador ATmega328P.

A circuit for temperature reading was designed using the LM35 sensor, the reading was shown by means of a multiplexer on 4 seven-segment displays (Anode and Common Cathode), for the development of the project the Arduino Uno card was used with the ATmega328P microcontroller.LECTOR DE TEMPERATURA CON LM35 Y MULTIPLEXOR DE DISPLAY DE 7 SEGMENTOS CON AR...

LECTOR DE TEMPERATURA CON LM35 Y MULTIPLEXOR DE DISPLAY DE 7 SEGMENTOS CON AR...Fernando Marcos Marcos

El desarrollo de la practica consiste en realizar un circuito con un transistor en configuración en base común y utilizar el transistor como un switch, se utilizaran led para ver que efectivamente funciona de esta manera, lo que se pretende es llevar al transistor, ya sea a su punto de corte o a su punto de saturación, así funcionara como switch. USO DEL TRANSISTOR COMO SWITCH - TRANSISTOR EN CORTE Y EN SATURACION - TRANSI...

USO DEL TRANSISTOR COMO SWITCH - TRANSISTOR EN CORTE Y EN SATURACION - TRANSI...Fernando Marcos Marcos

Diseño e complementación de un sistema de Monitoreo y control de humedad.

Antecedentes

En la Universidad Autónoma de Baja California ECITEC, en el área de Ingeniería en Renovables se ha implementado un proyecto coordinado por la Dr. Ma. Cristina Castañón el cual es llamado Vermicultura (Biotecnología para el desarrollo sostenible) el cual tiene como fin la producción de lombrices por medio de la lombricomposta. Para el buen desarrollo de las lombrices es importante considerar diversos factores químicos y físicos como lo son el nivel de oxigeno de la tierra, el potencial hídrico, la temperatura, la humedad, entre otros, el único factor que había sido controlado fue la humedad y de forma manual y empírica.

Justificación

Este proyecto ha sido implementado por el hecho de que el control de humedad no era muy efectivo por el hecho de ser de forma manual y debido a que la frecuencia de riego de la lombricomposta no era muy frecuente, lo que provocaba que los porcentajes de humedad de la lombricomposta variaran afectando el desarrollo de las lombrices, por ello se ha desarrollado el presente proyecto, para tener un control de humedad más eficiente, mejorando las condiciones físicas de la lombricomposta, y además ofreciendo al usuario un monitoreo en tiempo real de la humedad del lugar. SISTEMA DE CONTROL Y MONITOREO DE HUMEDAD EN LOMBRICOMPOSTA - HUMIDITY MONITO...

SISTEMA DE CONTROL Y MONITOREO DE HUMEDAD EN LOMBRICOMPOSTA - HUMIDITY MONITO...Fernando Marcos Marcos

Se realizó un circuito que cumpliera la función convertir una señal analógica a una señal digital utilizando integrados diseñados (ADC 0804) para ello.DISEÑO ANALOGICO Y ELECTRONICA - ADC - CONVERTIDOR ANALÓGICO DIGITAL - ANALOG...

DISEÑO ANALOGICO Y ELECTRONICA - ADC - CONVERTIDOR ANALÓGICO DIGITAL - ANALOG...Fernando Marcos Marcos

Más de Fernando Marcos Marcos (20)

LECTOR DE TEMPERATURA CON LM35 Y MULTIPLEXOR DE DISPLAY DE 7 SEGMENTOS CON AR...

LECTOR DE TEMPERATURA CON LM35 Y MULTIPLEXOR DE DISPLAY DE 7 SEGMENTOS CON AR...

Multiplexor Display de 7 Segmentos con Arduino UNO ATmega328P

Multiplexor Display de 7 Segmentos con Arduino UNO ATmega328P

CONTADOR BINARIO ASCENDENTE-DESCENDENTE DE 14 BITS CON ARDUINO

CONTADOR BINARIO ASCENDENTE-DESCENDENTE DE 14 BITS CON ARDUINO

CONTADOR BINARIO DESCENDENTE DE 14 BITS CON ARDUINO

CONTADOR BINARIO DESCENDENTE DE 14 BITS CON ARDUINO

CONTADOR BINARIO ASCENDENTE DE 14 BITS CON ARDUINO

CONTADOR BINARIO ASCENDENTE DE 14 BITS CON ARDUINO

CONTADOR BINARIO DESCENDENTE DE 8 BITS CON ARDUINO

CONTADOR BINARIO DESCENDENTE DE 8 BITS CON ARDUINO

DISEÑO DE PCB CON MODULO DE TRANSMISIÓN Y RECEPCIÓN RN41

DISEÑO DE PCB CON MODULO DE TRANSMISIÓN Y RECEPCIÓN RN41

DISEÑO Y DESARROLLO DE UNA PLACA PCB CON ATMEGA 328

DISEÑO Y DESARROLLO DE UNA PLACA PCB CON ATMEGA 328

PLL (OSCILADOR POR CAMBIO DE FASE) - PHASE SHIFT OSCILLATOR

PLL (OSCILADOR POR CAMBIO DE FASE) - PHASE SHIFT OSCILLATOR

USO DEL TRANSISTOR COMO SWITCH - TRANSISTOR EN CORTE Y EN SATURACION - TRANSI...

USO DEL TRANSISTOR COMO SWITCH - TRANSISTOR EN CORTE Y EN SATURACION - TRANSI...

SISTEMA DE CONTROL Y MONITOREO DE HUMEDAD EN LOMBRICOMPOSTA - HUMIDITY MONITO...

SISTEMA DE CONTROL Y MONITOREO DE HUMEDAD EN LOMBRICOMPOSTA - HUMIDITY MONITO...

DISEÑO ANALOGICO Y ELECTRONICA - ADC - CONVERTIDOR ANALÓGICO DIGITAL - ANALOG...

DISEÑO ANALOGICO Y ELECTRONICA - ADC - CONVERTIDOR ANALÓGICO DIGITAL - ANALOG...

Último

Último (20)

NTP- Determinación de Cloruros en suelos y agregados (1) (1).pptx

NTP- Determinación de Cloruros en suelos y agregados (1) (1).pptx

MODIFICADO - CAPITULO II DISEÑO SISMORRESISTENTE DE VIGAS Y COLUMNAS.pdf

MODIFICADO - CAPITULO II DISEÑO SISMORRESISTENTE DE VIGAS Y COLUMNAS.pdf

LA APLICACIÓN DE LAS PROPIEDADES TEXTUALES A LOS TEXTOS.pdf

LA APLICACIÓN DE LAS PROPIEDADES TEXTUALES A LOS TEXTOS.pdf

TEXTO UNICO DE LA LEY-DE-CONTRATACIONES-ESTADO.pdf

TEXTO UNICO DE LA LEY-DE-CONTRATACIONES-ESTADO.pdf

Circuitos Digitales - Contador Digital

- 1. TABLAS PARA EL CONTADOR DE LAS UNIDADES TABLA DE ESTADOS Actual Salida Sig. Edo. A 0000 B B 0001 C C 0010 D D 0011 E E 0100 F F 0101 G G 0110 H H 0111 I I 1000 J J 1001 A TABLA DE EXCITACIÓN Estado Actual Salida Estados Siguiente Q3 Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 1 0 1 1 1 0 1 1 1 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 1 1 0 0 1 1 0 0 1 0 0 0 0 Lo que se pretende hacer es lo siguiente: TABLA DE EXCITACIÓN DEL JK J K 𝑸 𝒕+𝟏 𝑸 𝒕+𝟏 ̅̅̅̅̅̅ 0 0 0 0 1 X 0 1 X 1 1 0 0 0 1 1

- 2. 1ero: Se realizaran dos circuitos para la solución del problema. 2do: El primercontadorserá para lasunidades,que cuente de 0hasta 9, peroen binario,llegandoa 9 se regresara el contador a 0 y asi continuamente. 3ero: El segundocontadorserápara lasdecenas,que cuente de 0 hasta 5, peroen binario,llegando a 5 se regresara el contador a 0 y así continuamente. ** El contador de las decenas se activara solo cuando el contador de unidades llegue hasta 9 y así sucesivamente. TABLA DE KARNAUGHT PARA EL CONTADOR DE LAS UNIDADES J0=1 Q1 Q3 Q0 Q2 00 01 11 10 00 1 X X 1 01 1 X X 1 11 X X X X 10 1 X X X J1=𝑸𝟑̅̅̅̅ Q0 Q1 Q3 Q0 Q2 00 01 11 10 00 0 1 X 0 01 0 1 X 0 11 X X X X 10 0 X X X K0=1 Q1 Q3 Q0 Q2 00 01 11 10 00 X 1 1 X 01 X 1 1 X 11 X X X X 10 X 1 X X K1=Q1 Q0 Q1 Q3 Q0 Q2 00 01 11 10 00 0 X 1 0 01 0 X 1 0 11 X X X X 10 0 X X X

- 3. J2= Q1 Q0 Q1 Q3 Q0 Q2 00 01 11 10 00 0 0 1 0 01 0 0 X 0 11 X X X X 10 0 0 X X J3=Q2 Q1 Q0 Q1 Q3 Q0 Q2 00 01 11 10 00 0 0 0 0 01 0 0 1 0 11 X X X X 10 0 X X X K2= Q1 Q0 Q1 Q3 Q0 Q2 00 01 11 10 00 0 0 X 0 01 0 0 1 0 11 X X X X 10 0 0 X X K3= Q3 Q0 Q1 Q3 Q0 Q2 00 01 11 10 00 0 0 0 0 01 0 0 X 0 11 X X X X 10 0 1 X X

- 4. TABLAS PARA EL CONTADOR DE LAS DECENAS. TABLA DE ESTADOS Actual Salida Sig. Edo. A 000 B B 001 C C 010 D D 011 E E 100 F F 101 A TABLA DE EXCITACIÓN Estado Actual Salida Estados Siguiente Q3 Q2 Q1 Q0 Q2 Q1 Q0 Q2 Q1 Q0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 1 0 0 1 0 0 1 0 0 1 0 1 1 0 1 1 0 1 0 0 0 TABLA DE EXCITACIÓN DEL JK J K 𝑸 𝒕+𝟏 𝑸 𝒕+𝟏 ̅̅̅̅̅̅ 0 0 0 0 1 X 0 1 X 1 1 0 0 0 1 1

- 5. TABLAS DEKARNAUGHT PARA EL CONTADOR DE LAS DECENAS. J0=1 Q1 Q3 Q0 Q2 00 01 11 10 00 1 X X 1 01 1 X X X J1= 𝑄2̅̅̅̅ Q0 Q1 Q3 Q0 Q2 00 01 11 10 00 0 1 X 0 01 0 0 X X J2= Q1 Q0 Q1 Q3 Q0 Q2 00 01 11 10 00 0 0 1 0 01 0 X X X K0=1 Q1 Q3 Q0 Q2 00 01 11 10 00 X 1 1 X 01 X 1 X X K1= Q1 Q0 Q1 Q3 Q0 Q2 00 01 11 10 00 0 0 1 0 01 0 0 X X K2= Q2 Q0 Q1 Q3 Q0 Q2 00 01 11 10 00 0 0 X 0 01 0 1 X X

- 6. AHORA CON LAS ECUACIONES OBTENIDAS SE PROSIGUE A SIMULAR LOS CIRCUITOS PARA COMPROBAR QUE EFECTIVAMENTE REALIZAN LA FUNCION QUE SE DESEA. Ecuaciones obtenidas para el contador de unidades (Con estas ecuaciones se realizaran los circuitos): J0=1 K0=1 J1=𝑄3̅̅̅̅ Q0 K1=Q1 Q0 J2= Q1 Q0 K2= Q1 Q0 J3=Q2 Q1 Q0 K3= Q3 Q0 Ecuaciones obtenidas para el contador de decenas (Con estas ecuaciones se realizaran los circuitos): J0=1 K0=1 J1= 𝑄2̅̅̅̅ Q0 K1= Q1 Q0 J2= Q1 Q0 K2= Q2 Q0 U1 DCD_HEX U2A 74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1V1 60 Hz 5 V VCC 5V VCC 5V VCC 5V VCC 5V U3A 74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U4A 74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U5A 74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U7A 74LS09D U6A 74LS09D U8A74LS09D U9A 74LS09D U10A 74LS05N U2A 74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 VCC 5V U3A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U4A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 V1 60 Hz 5 V VCC 5V VCC 5V U7A 74LS09D U1A 74LS09D U5A74LS09D U6 DCD_HEX U10A 74LS05N VCC 5V

- 7. El circuito completo sin codificador se muestra en el siguiente diagrama: El circuito completo con codificador se muestra en el siguiente diagrama: U1 DCD_HEX U2A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1V1 170 Hz 5 V VCC 5V VCC 5V VCC 5V VCC 5V U3A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U4A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U5A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U7A 74LS09D U6A 74LS09D U8A74LS09D U9A 74LS09D U10A 74LS05N U11A 74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 VCC 5V VCC 5V VCC 5V VCC 5V U12A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U13A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U14A 74LS09D U15A 74LS09D U16A74LS09D U17 DCD_HEX U18A 74LS09D U2A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1V1 170 Hz 5 V VCC 5V VCC 5V VCC 5V VCC 5V VCC 5V VCC 5V VCC 5V VCC 5V U3A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U4A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U5A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U7A 74LS09D U6A 74LS09D U8A74LS09D U9A 74LS09D U10A 74LS05N U11A 74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U12A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U13A74LS112N 1Q 5 ~1Q 6 ~1PR 4 1K2 ~1CLR 15 1J3 1CLK1 U14A 74LS09D U15A 74LS09D U16A74LS09D U18A 74LS09D U19 74LS48N A7 B1 C2 D6 OA 13 OD 10 OE 9 OF 15 OC 11 OB 12 OG 14 ~LT3 ~RBI5 ~BI/RBO4 U1 74LS48N A7 B1 C2 D6 OA 13 OD 10 OE 9 OF 15 OC 11 OB 12 OG 14 ~LT3 ~RBI5 ~BI/RBO4 U17 A B C D E F G CK U20 A B C D E F G CK